Datasheet 搜索 > 32位控制器 > NXP(恩智浦) > LPC2148FBD64 数据手册 > LPC2148FBD64 开发手册 4/24 页

器件3D模型

器件3D模型¥ 152.611

LPC2148FBD64 开发手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

32位控制器

封装:

LQFP-64

描述:

NXP LPC2148FBD64 微控制器(MCU), 16/32位, ARM7, 512K闪存, 64LQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

应用领域在P23

导航目录

LPC2148FBD64数据手册

Page:

of 24 Go

若手册格式错乱,请下载阅览PDF原文件

NXP Semiconductors

AN10878

Migrating to the LPC1700 series

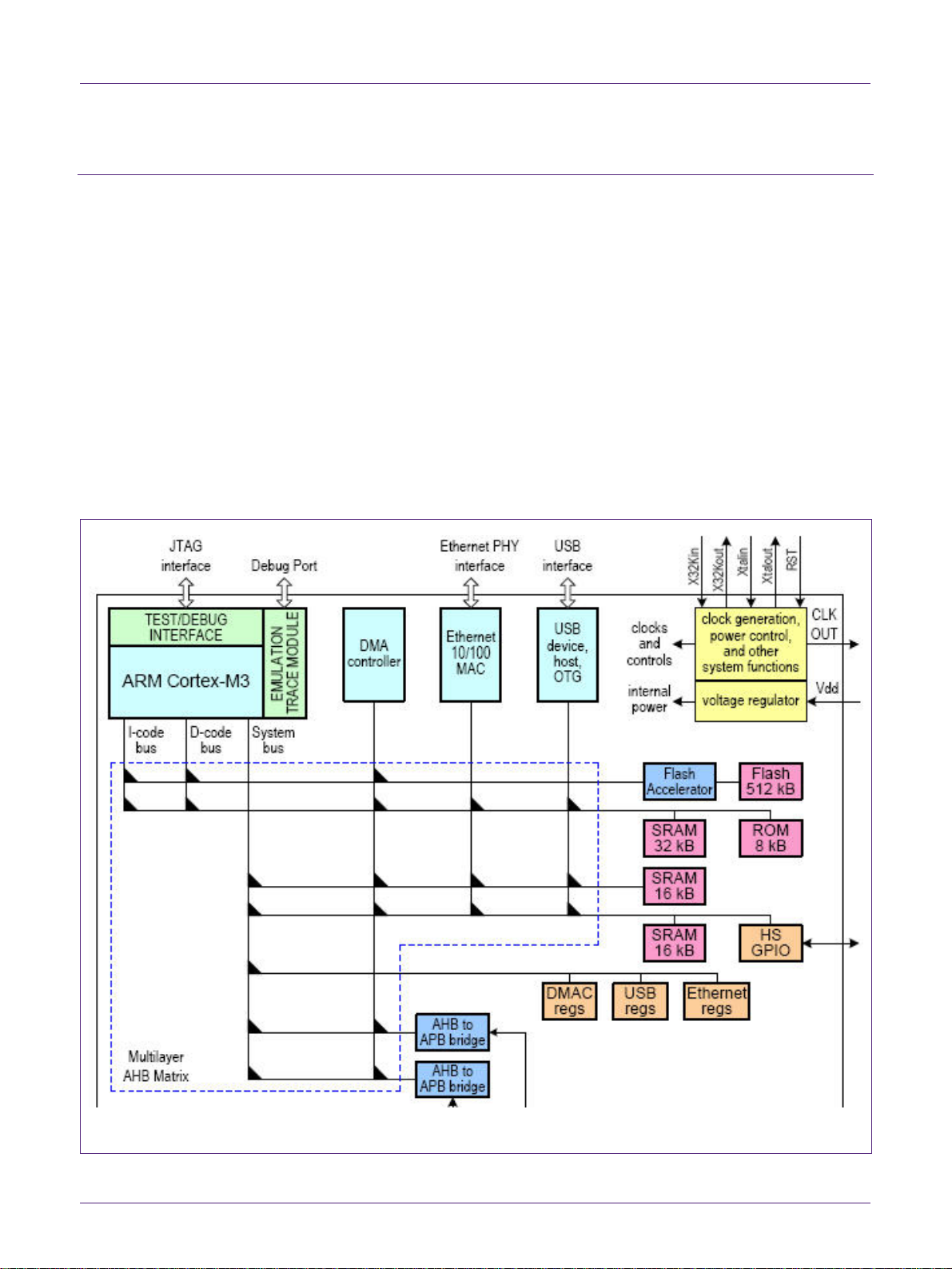

2. Multilayer AHB matrix and split APB bus

2.1 Multilayer AHB (Advanced High-performance Bus) matrix

The ARM7-based microcontrollers (LPC2300/2400) utilize a dual AHB bus architecture

which allows simultaneous operations from the following modules.

1. CPU operation from internal memory

2. USB operation with dedicated DMA

3. Ethernet operation with dedicated DMA

4. General purpose DMA operation from peripherals that can support DMA

The LPC1700 has been enhanced by adding a multi-layer AHB matrix to connect the

Cortex-M3 buses and other bus masters to peripherals in a flexible manner that

optimizes performance by allowing peripherals on different slave ports of the matrix to be

accessed simultaneously by different bus masters.

Details of the multilayer AHB matrix connections are shown below:

Fig 1. LPC1700 block diagram (top)

AN10878_1 © NXP B.V. 2009. All rights reserved.

Application note Rev. 01 — 6 October 2009 4 of 24

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件