Datasheet 搜索 > 接口芯片 > Maxim Integrated(美信) > MAX3232CSE 数据手册 > MAX3232CSE 开发手册 6/9 页

器件3D模型

器件3D模型¥ 7.181

MAX3232CSE 开发手册 - Maxim Integrated(美信)

制造商:

Maxim Integrated(美信)

分类:

接口芯片

封装:

SOIC-16

描述:

3.0V至5.5V ,低功耗,高达1Mbps ,真RS - 232收发器,使用四只0.1μF外部电容 3.0V to 5.5V, Low-Power, up to 1Mbps, True RS-232 Transceivers Using Four 0.1レF External Capacitors

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

MAX3232CSE数据手册

Page:

of 9 Go

若手册格式错乱,请下载阅览PDF原文件

touches an I/O port. The discharges accompanying these routine events can render an I/O port useless by

destroying one or more interface ICs connected to the port. These failures can be expensive in terms of

both warranty repairs and perceived quality.

ESD can cause further damage to manufacturers, since equipment manufacturers may soon be barred

from selling to the European Community if their equipment fails to meet minimum levels of ESD

performance, as spelled out by IEC 801-2.

These two factors have led Maxim to develop a family of RS-232 products with ±15kV of ESD protection

(Table A). These interface ICs are the only ones to specify and achieve ±15kV ESD protection using both

the human body model and the IEC 801-2 air-gap discharge method. Maxim's high-ESD protection

eliminates the need for costly external protection devices such as TransZorb, while preventing expensive

field failures.

Table A. RS-232-interface ICs with ±15kV ESD Protection

Device

No. of

Drivers/

Receivers

ESD Level (kV)

Capacitor

Value

(mF)

Latchup

Free

Data

Rate

(kbps)

No. of

Active

Receivers

in SHDN

SHDN

I

CC

(mA)

Price

1000

pc.

(S)

Human

Body

Model

IEC 801-2

Contact

Discharge

Air-Gap

Discharge

MAX202E 2/2 ±15 ±8 ±15 0.1 Yes 120 0 N/A 1.85

MAX211E 4/5 ±15 ±8 ±15 0.1 Yes 120 0 1 3.62

MAX213E 4/5 ±15 ±8 ±15 0.1 Yes 120 2 15 3.62

MAX232E 2/2 ±15 ±8 ±15 1.0 Yes 120 0 N/A 1.85

MAX241E 4/5 ±15 ±8 ±15 1.0 Yes 120 0 1 3.62

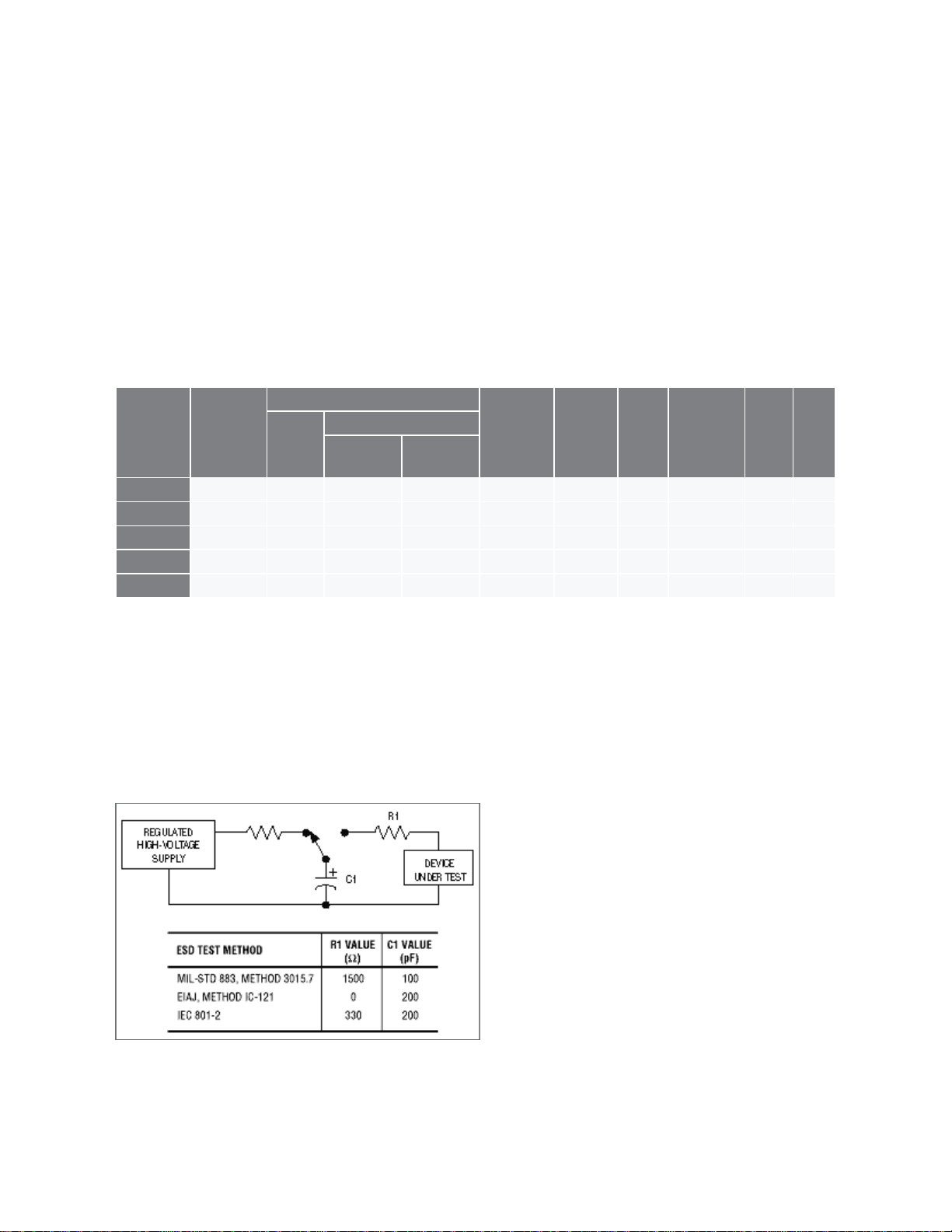

Older ESD Test Methods

Two methods have been commonly used for testing the ESD susceptibility of integrated circuits. The

oldest, method 3015.7 of MIL-standard 883 (also known as the human body model), was developed to aid

manufacturers in understanding the precautions necessary for packaging and handling ICs. This method

tests each package pin against all other pins, and classifies a device according to the voltage at which the

first failure occurs (which is usually on the pin most susceptible to ESD). The applied ESD waveform is

derived from a circuit called the human body model (Figure A). The capacitance (100pF) models that of the

human body, and the resistance (1500Ω) models the typical series resistance in the discharge path that

includes the body, the IC, and ground.

Figure A. Most ESD standards specify the same test circuit, but with different component values.

Page 6 of 9

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件