Datasheet 搜索 > 微处理器 > Freescale(飞思卡尔) > MPC8308CVMAGD 数据手册 > MPC8308CVMAGD 开发手册 1/2 页

器件3D模型

器件3D模型¥ 7.196

MPC8308CVMAGD 开发手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

分类:

微处理器

封装:

MAPBGA-473

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P1

导航目录

MPC8308CVMAGD数据手册

Page:

of 2 Go

若手册格式错乱,请下载阅览PDF原文件

Overview

The MPC8308 is a cost-effective, low-

power, highly integrated PowerQUICC

®

II Pro

processor designed to address the

requirements of networking applications

such as smart grid home energy gateways,

data concentrators, wireless LAN access

points, wireless femto base stations and

industrial applications such as industrial

control and factory automation. It extends the

PowerQUICC II Pro family by balancing the

higher MIPS/MHz performance provided by

the e300 core with low power consumption at

a very aggressive price.

For networking applications, the Gigabit

Ethernet MACs support connectivity to

the wired network while the PCI Express

®

and SDIO interfaces can offer connectivity

to wireless LAN or 3G and 4G modem

devices. The MPC8308 processor features

integrated IEEE

®

1588 time synchronization

for applications such as time-sensitive

telecommunications services, industrial

network switches, powerline networks and

test/measurement devices. All of these

applications will be fully enabled with the

MPC8308 processor and the low-cost

evaluation board with optimized Linux

®

BSP

and drivers. Freescale also works with third-

party partners to enable application software

for end user interfaces.

Core Complex

The MPC8308 processor incorporates the

e300c3 (603e core compatible) core at

266, 333 and 400 MHz with 1.92 DMIPS/

MHz. The core, built on Power Architecture

®

technology, includes dual integer units

as well as a modified multiply instruction.

These architectural enhancements enable

more efficient operations to be executed in

parallel, resulting in a significant performance

improvement. The e300 core complex

also includes 16 KB each of L1 instruction

and data caches and on-chip memory

management units (MMUs) with dual integer

units and SP/DP FPU.

Integrated Communication Processors

MPC8308 PowerQUICC

®

II Pro Processor

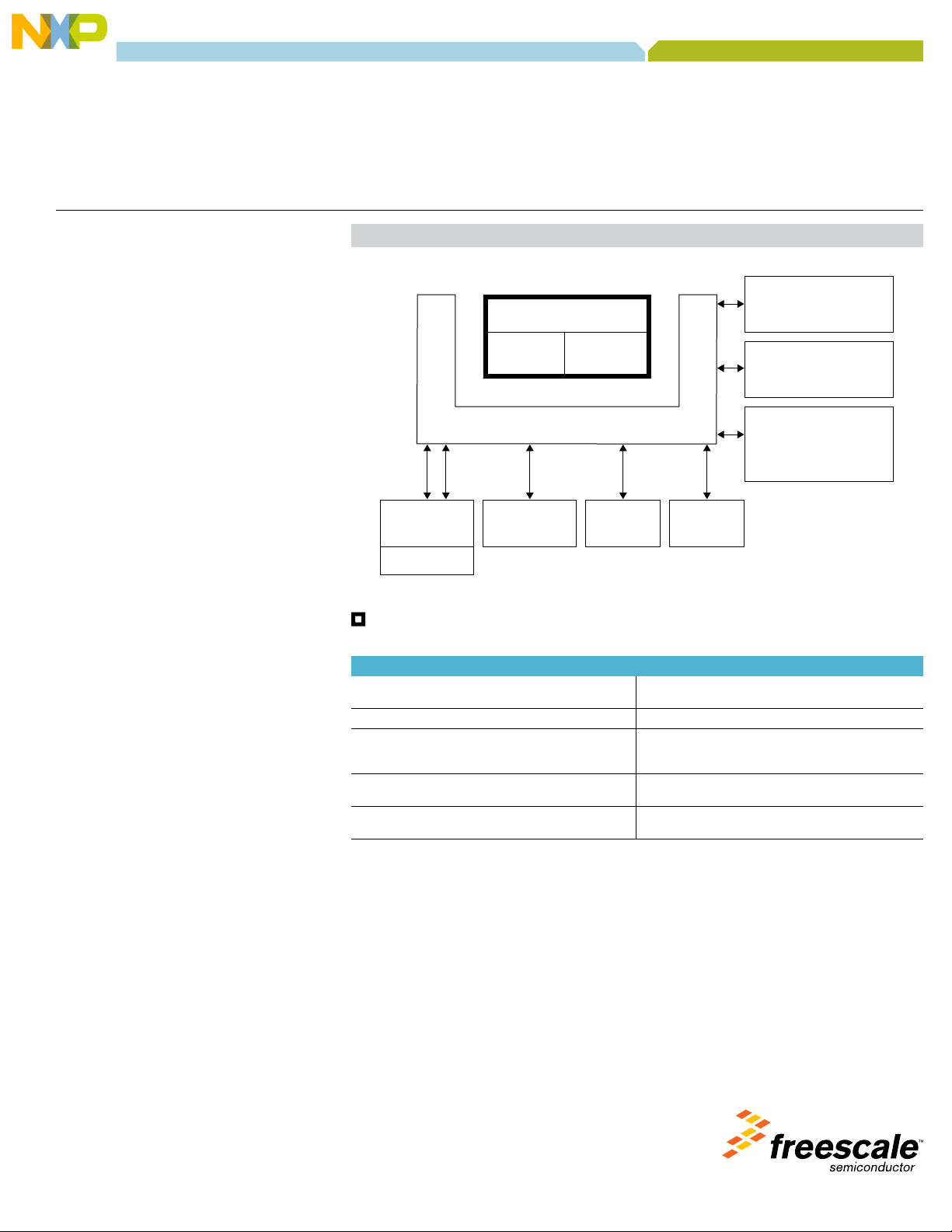

MPC8308 Block Diagram

USB 2.0

Coherent System Bus

2 x RGMII/MII

DDR2 SDRAM

Controller

Local Bus

PCI

Express

®

eSDHCeSDHC

2 x Gigabit

Ethernet

DUART, 2 x I

2

C, SPI,

Timers, GPIO,

Interrupt Control

16 KB

I-Cache

e300 Core

16 KB

D-Cache

Core

Features

Benefits

High-performance e300 core, built on Power

Architecture

®

technology, at 1.92 DMIPS/MHz

High-efficiency core means less MHz needed to get the

job done or extra CPU headroom to perform other tasks

Comprehensive third-party ecosystem

Faster time to market

Migration path

Improved performance/cost migrating from

PowerQUICC

®

or PowerQUICC II.

Common architecture eases migration.

Best-in-class power consumption

Enables fanless, “green” and low-cost designs,

and improves reliability

Integrated Gigabit Ethernet, USB, SD/MMC controller,

IEEE

®

1588v2, PCI Express

®

interfaces

Allows the flexibility to address a wide range of

applications and reduced system cost

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件