Datasheet 搜索 > 微控制器 > ST Microelectronics(意法半导体) > STM32F101R6T6A 数据手册 > STM32F101R6T6A 开发手册 5/12 页

器件3D模型

器件3D模型¥ 17.047

STM32F101R6T6A 开发手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

微控制器

封装:

LQFP-64

描述:

STMICROELECTRONICS STM32F101R6T6A 微控制器, 32位, ARM 皮质-M3, 36 MHz, 32 KB, 6 KB, 64 引脚, LQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

技术参数、封装参数在P12

应用领域在P12

型号编号列表在P1

导航目录

STM32F101R6T6A数据手册

Page:

of 12 Go

若手册格式错乱,请下载阅览PDF原文件

DocID13529 Rev 4 5/12

AN2548 Performance considerations

12

data processing interleaved with data accesses. This allows a natural interleaving of DMA

and CPU accesses to RAM, which results most of the time in an almost transparent DMA

mode, the effect of DMA transfer over the CPU execution time being minimal.

The inherent parallelism of the STM32F1x/L1x bus structure, associated with the DMA bus-

stealing mechanism ensure that the CPU is not stuck for long periods of time waiting to read

data from the SRAM. DMAs with bus stealing mechanism consequently use the bus in a

more efficient way, thus significantly contributing to reduce the total software execution time.

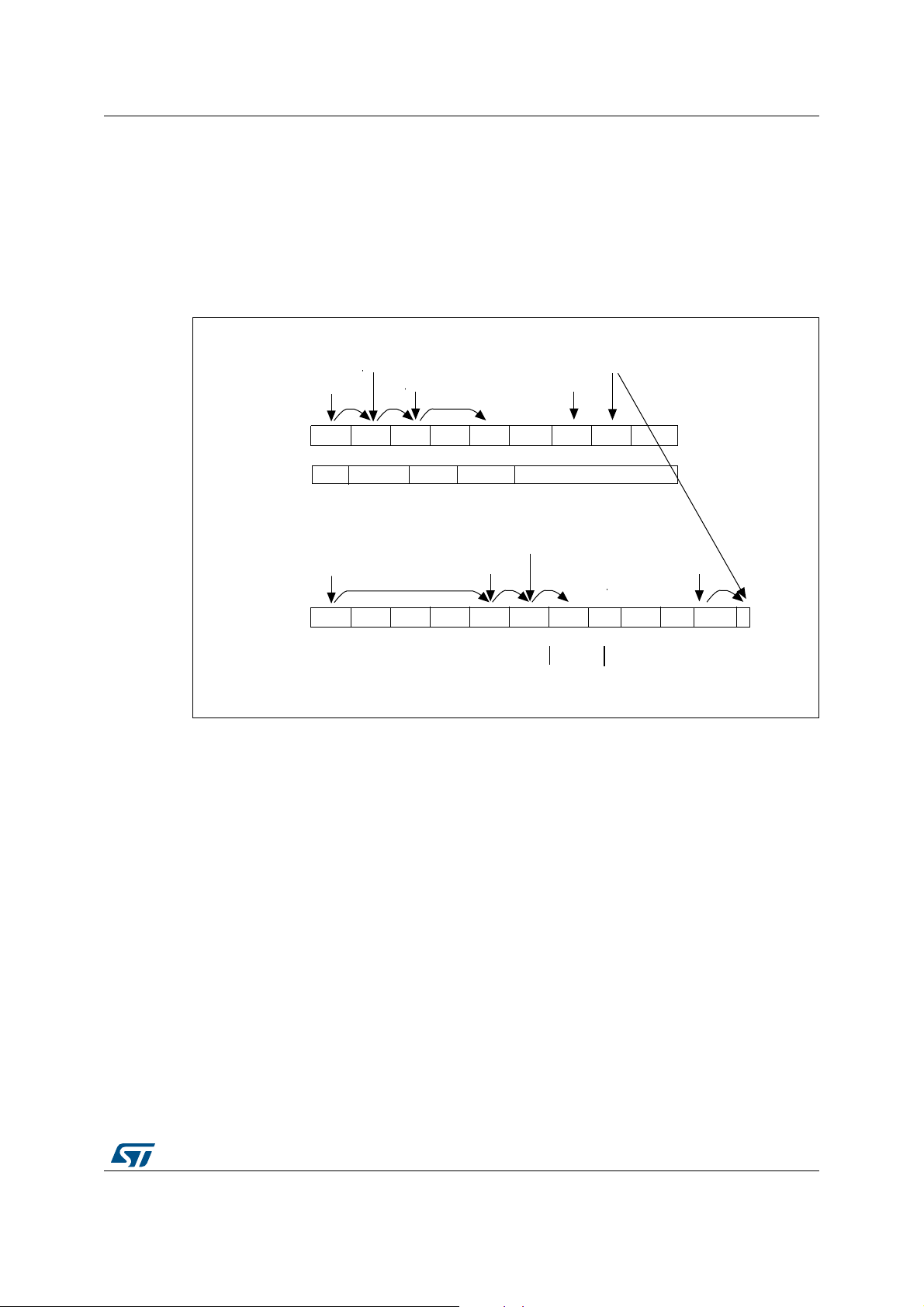

Figure 1. Bus stealing vs. burst mode for DMA transfer

2.3 DMA latency

Three operations are required to perform a DMA data transfer from peripheral to SRAM

memory. For example, when storing ADC continuous conversion data in SRAM, the

following steps must be followed:

1. DMA request arbitration & address computation

2. Reading data from the peripheral (DMA source)

3. Writing loaded data in SRAM (DMA destination)

When transferring data from SRAM to peripheral (for example SPI transmission), the

operations are performed in the opposite order:

1. DMA request arbitration & address computation

2. Reading data from SRAM memory (DMA source)

3. Writing data to the peripheral through the APB bus (DMA destination)

The service time per channel, t

S

, is given by the equation below:

AI

32!-

!0"

$-! $-!

#05RQ

#05

#05

$-!DATATRANSFERSUSINGBUSSTEALING

32!-

!0"

#05RQ

$-! #05

#05RQ

#05STALL

%NDOF37EXECUTION

#05

#05STALL

#05RQ

$-!

$-!

#05RQ

#05RQ #05RQ

$-!DATATRANSFERSUSINGBURSTMODE

$-! $-!$-! $-!#05#05 #05

$-!

#05RQ

$-!

$-!

t

S

t

A

t

Acc

t+

SRAM

+=

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件