Datasheet 搜索 > 微控制器 > ST Microelectronics(意法半导体) > STM32F372V8H6 数据手册 > STM32F372V8H6 数据手册 26/128 页

¥ 32.579

STM32F372V8H6 数据手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

微控制器

封装:

BGA-100

描述:

STMICROELECTRONICS STM32F372V8H6 微控制器, 32位, 浮点单元, ARM 皮质-M4F, 72 MHz, 64 KB, 16 KB, 100 引脚, BGA

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

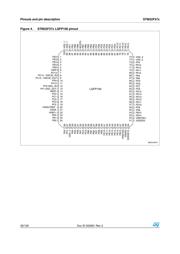

引脚图在P28P29P30P31P32P33P34P35P36P37P38P39Hot

典型应用电路图在P73P75P98

原理图在P11

封装尺寸在P113

型号编码规则在P122P123P124

封装信息在P113P114P115P116P117P118P119P120P121P122P123

技术参数、封装参数在P53

应用领域在P128

电气规格在P50P51P52P53P54P55P56P57P58P59P60P61

导航目录

STM32F372V8H6数据手册

Page:

of 128 Go

若手册格式错乱,请下载阅览PDF原文件

Functional overview STM32F37x

26/128 Doc ID 022691 Rev 3

master mode, the master clock can be output to the external DAC/CODEC at 256 times the

sampling frequency.

Refer to Ta bl e 9 for the features between SPI1 and SPI2.

3.22 High-definition multimedia interface (HDMI) - consumer

electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the

Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an

environment. It is specified to operate at low speeds with minimum processing and memory

overhead. It has a clock domain independent from the CPU clock, allowing the HDMI_CEC

controller to wakeup the MCU from Stop mode on data reception.

3.23 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It

can receive and transmit standard frames with 11-bit identifiers as well as extended frames

with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and

14 scalable filter banks.

3.24 Universal serial bus (USB)

The STM32F37x embeds an USB device peripheral compatible with the USB full-speed 12

Mbs. The USB interface implements a full-speed (12 Mbit/s) function interface. It has

software-configurable endpoint setting and suspend/resume support. The dedicated 48

MHz clock is generated from the internal main PLL (the clock source must use a HSE

crystal oscillator).

Table 9. STM32F37x SPI/I2S implementation

SPI features

(1)

1. X = supported.

SPI1 SPI2 SPI3

Hardware CRC calculation X X X

Rx/Tx FIFO X X X

NSS pulse mode X X X

I2S mode XXX

TI mode XXX

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件