Datasheet 搜索 > AD转换器 > ADI(亚德诺) > AD7768BSTZ 数据手册 > AD7768BSTZ 其他数据使用手册 1/72 页

器件3D模型

器件3D模型¥ 149.657

AD7768BSTZ 其他数据使用手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

AD转换器

封装:

LQFP-64

描述:

ANALOG DEVICES AD7768BSTZ Analogue to Digital Converter, 8-CH, 24 bit, 256 kSPS, Single, Dual (+/-), 2.25 V, 5 V, LQFP 新

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P17Hot

典型应用电路图在P36

原理图在P1

封装尺寸在P72

型号编码规则在P72

功能描述在P3P17

技术参数、封装参数在P1P4P6P9P12P13P16P57

应用领域在P1P36

电气规格在P21

导航目录

AD7768BSTZ数据手册

Page:

of 72 Go

若手册格式错乱,请下载阅览PDF原文件

8-Channel, 24-Bit, Simultaneous Sampling

ADC with Power Scaling, 110.8 kHz BW

Data Sheet

AD7768

Rev. 0 Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2016 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

FEATURES

Precision ac and dc performance

8-channel simultaneous sampling

256 kSPS ADC output data rate per channel

108 dB dynamic range

110.8 kHz input bandwidth (−3 dB bandwidth (BW))

−120 dB THD typical

±2 ppm INL, ±50 μV offset error, ±30 ppm gain error

Optimized power dissipation vs. noise vs. input bandwidth

Selectable power, speed, and input bandwidth

Fast: highest speed; 110.8 kHz BW, 51.5 mW per channel

Median: half speed, 55.4 kHz BW, 27.5 mW per channel

Eco: lowest power, 13.8 kHz BW, 9.375 mW per channel

Input BW range: dc to 110.8 kHz

Programmable input bandwidth/sampling rates

Cyclic redundancy check (CRC) error checking on data interface

Daisy-chaining

Linear phase digital filter

Low latency sinc5 filter

Wideband brick wall filter: ±0.005 dB ripple to 102.4 kHz

Analog input precharge buffers

Power supply

AVDD1 = 5 V, AVDD2 = 2.25 V to 5 V

IOVDD = 2.5 V to 3.3 V or IOVDD = 1.8 V

64-lead LQFP package, no pad

Temperature range: −40°C to +105°C

APPLICATIONS

Data acquisition systems: USB/PXI/Ethernet

Instrumentation and industrial control loops

Audio test and measurement

Vibration and asset condition monitoring

3-phase power quality analysis

Sonar

High precision medical EEG/EMG/ECG

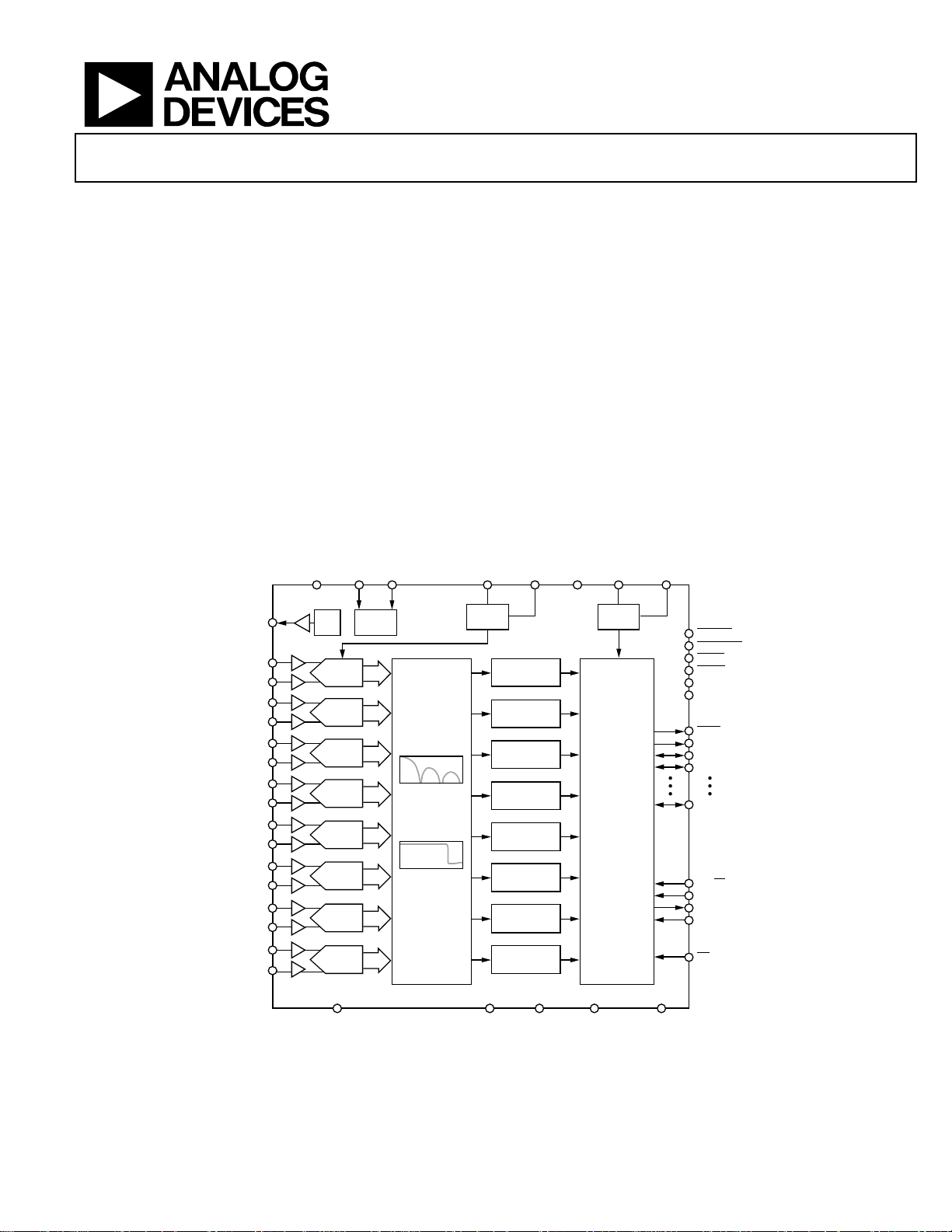

FUNCTIONAL BLOCK DIAGRAM

ADC

OUTPUT

DATA

SERIAL

INTERFACE

DIGITAL

FILTER

ENGINE

WIDEBAND

LOW RIPPLE

FILTER

SINC5

LOW LATENCY

FILTER

SPI

CONTROL

INTERFACE

1.8V

LDO

SYNC_IN

1.8V

LDO

BUFFERED

VCM

VCM

AIN1+

CH 1

AIN1–

AIN2+

CH 2

AIN2–

AIN3+

CH 3

AIN3–

AIN4+

CH 4

AIN4–

AIN5+

CH 5

AIN5–

AIN6+

CH 6

AIN6–

AIN7+

CH 7

AIN7–

AIN0+

CH 0

AIN0–

VCM ×8

PRECHARGE

REFERENCE

BUFFERS

SYNC_OUT

START

RESET

FORMAT1

FORMAT0

DRDY

DCLK

DOUT0

DOUT1

ST0/CS

PIN/SPI

ST1/SCLK

DEC0/SDO

DEC1/SDI

DOUT7

AVSS XTAL2/MCLK XTAL1 MODE3/GPIO3

TO

MODE0/GPIO0

FILTER/GPIO4

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

Σ-∆

ADC

AVDD1 DGND

AD7768

IOVDD DREGCAP

REGC

A

P

A

/

REGCAPB

A

V

DD2A/

AVDD2B

REFx+ REFx–

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

OFFSET,

GAIN PHASE

CORRECTION

14001-001

Figure 1.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件