Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > ATMEGA162V-8AU 数据手册 > ATMEGA162V-8AU 其他数据使用手册 3/8 页

器件3D模型

器件3D模型¥ 7.182

ATMEGA162V-8AU 其他数据使用手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

TQFP-44

描述:

ATmega 系列 8 MHz 16 KB 闪存 1 KB SRAM 8 位 微控制器 - TQFP-44

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

功能描述在P1P6

导航目录

ATMEGA162V-8AU数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

3

AVR082

2516D–AVR–01/04

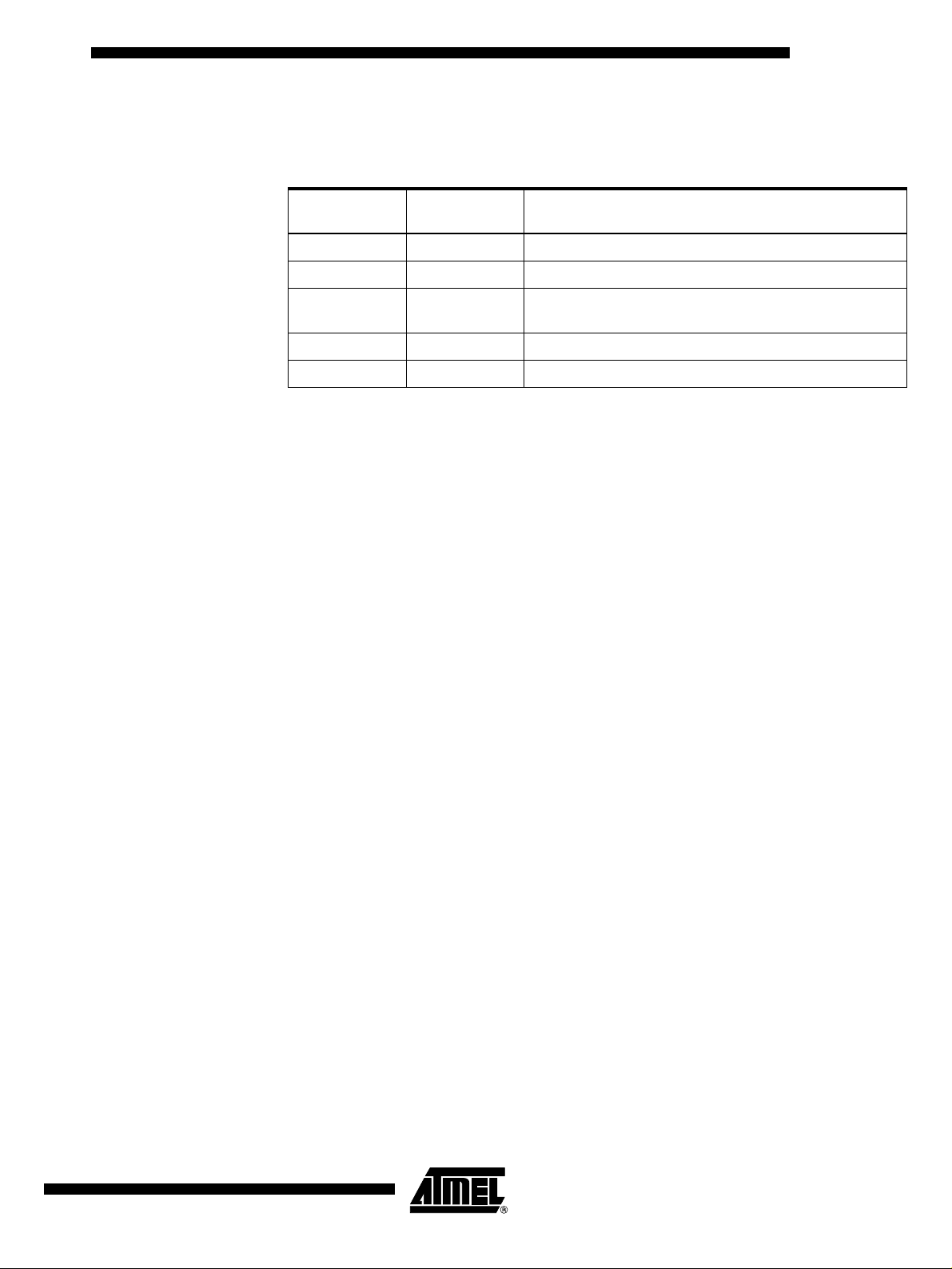

The following I/O Registers have changed names, but include the same functionality

and placement when accessed as in ATmega161:

Improvements to

Timer/Counters

For details about the improved and additional features, please refer to the data sheet.

The following features have been added:

• Variable top value in PWM mode.

• Timer/Counter0 extended with compare function and PWM.

• For Timer/Counter1, Phase and Frequency Correct PWM mode in addition to the

Phase Correct PWM mode.

Updating of OCR in PWM

Mode (Applies to all

Timer/Counters)

In PWM mode, the value written to the Output Compare Register is not physically used

as compare value until the Timer/Counter reaches the value TOP. The interpretation of

this point of time differs between ATmega161 and ATmega162. In ATmega161, the new

OCR value is used in the cycle where the Timer/Counter has the value TOP. In

ATmega162, the counter value TOP is used to update the compare value, i.e., it is first

active in the cycle where the Timer/Counter has the value TOP-1 down-counting.

Improvements to

External Memory

Interface

Refer to the ATmega162 data sheet for details on the changed timing.

Improvements to

UART

The UART in ATmega161 has been replaced by a USART in ATmega162. The

ATmega162 USART is compatible with the ATmega161 UART with one exception: The

two-level Receive Register acts as a FIFO. The FIFO is disabled when the M161C Fuse

is programmed. Still the following must be kept in mind when the M161C Fuse is

programmed:

• The UDR must only be read once for each incoming data.

• The Error Flags (FE and DOR) and the ninth data bit (RXB8) are buffered with the

data in the receive buffer. Therefore the status bits must always be read before the

UDR Register is read. Otherwise, the error status will be lost.

ATmega161 contains the baud-rate high-bytes for both UARTs in a common register –

UBRRHI. ATmega162 has separate registers for the high-bytes of the two USARTs;

UBRR0H and UBRR1H, implying a modification to the code when porting the design to

ATmega162

Another minor difference is the initial value of RXB8, which is “1” in the UART in

ATmega161 and “0” in the USART in ATmega162.

Table 3. Changed Register Names

Register name

in ATmega161

Register name

in ATmega162 Comments

GIMSK GICR

MCUSR MCUCSR

UBRRHI UBRR0H and

UBRR1H

Shared register split into two registers. See

“Improvements to UART” on page 3.

UBRR0 UBRR0L

UBRR1 UBRR1L

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件