Datasheet 搜索 > 微控制器 > Microchip(微芯) > DSPIC33EV256GM106T-I/MR 数据手册 > DSPIC33EV256GM106T-I/MR 其他数据使用手册 1/506 页

器件3D模型

器件3D模型¥ 29.531

DSPIC33EV256GM106T-I/MR 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-64

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P5P6P7P8P9P10P11P12P22P152P153P155Hot

原理图在P17P26P96P115P128P147P177P179P180P181P185P193

封装尺寸在P465P494

标记信息在P463P464

封装信息在P344P463P466P467P468P475P476P477P478P479P480P481

功能描述在P193P289

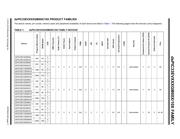

技术参数、封装参数在P288P345P350P351P353P355P394P395P396P397P398P399

应用领域在P2P241

电气规格在P22P88P155P225P227P288P291P328P351P352P409P494

导航目录

DSPIC33EV256GM106T-I/MR数据手册

Page:

of 506 Go

若手册格式错乱,请下载阅览PDF原文件

2013-2019 Microchip Technology Inc. DS70005144H-page 1

dsPIC33EVXXXGM00X/10X FAMILY

Operating Conditions

• 4.5V to 5.5V, 0°C to +85°C, DC to 70 MIPS

• 4.5V to 5.5V, -40°C to +125°C, DC to 60 MIPS

• 4.5V to 5.5V, -40°C to +150°C, DC to 40 MIPS

Core: 16-Bit dsPIC33E CPU

• Code-Efficient (C and Assembly) Architecture

• 16-Bit Wide Data Path

• Two 40-Bit Wide Accumulators

• Single-Cycle (MAC/MPY) with Dual Data Fetch

• Single-Cycle, Mixed-Sign MUL plus Hardware

Divide

• 32-Bit Multiply Support

• Intermediate Security for Memory:

- Provides a Boot Flash Segment in addition to

the existing General Flash Segment

• Error Code Correction (ECC) for Flash

• Added Two Alternate Register Sets for Fast

Context Switching

Clock Management

• Internal, 15% Low-Power RC (LPRC) – 32 kHz

• Internal, 1% Fast RC (FRC) – 7.37 MHz

• Internal, 10% Backup FRC (BFRC) – 7.37 MHz

• Programmable PLLs and Oscillator Clock Sources

• Fail-Safe Clock Monitor (FSCM)

• Additional FSCM Source (BFRC), Intended to

Provide a Clock Fail Switch Source for the

System Clock

• Independent Watchdog Timer (WDT)

• System Windowed Watchdog Timer (DMT)

• Fast Wake-up and Start-up

Power Management

• Low-Power Management modes (Sleep, Idle

and Doze)

• Power Consumption Minimized Executing

NOP String

• Integrated Power-on Reset (POR) and Brown-out

Reset (BOR)

• 0.5 mA/MHz Dynamic Current (typical)

• 50 µA at +25°C I

PD Current (typical)

PWM

• Up to Six Pulse-Width Modulation (PWM) Outputs

(three generators)

• Primary Master Time Base Inputs allow

Time Base Synchronization from Internal/External

Sources

• Dead Time for Rising and Falling Edges

• 7.14 ns PWM Resolution

• PWM Support for:

- DC/DC, AC/DC, inverters, Power Factor

Correction (PFC) and lighting

- Brushless Direct Current (BLDC), Permanent

Magnet Synchronous Motor (PMSM),

AC Induction Motor (ACIM), Switched

Reluctance Motor (SRM)

- Programmable Fault inputs

- Flexible trigger configurations for

Analog-to-Digital conversion

- Supports PWM lock, PWM output chopping

and dynamic phase shifting

Advanced Analog Features

• ADC module:

- Configurable as 10-bit, 1.1 Msps with

four S&H or 12-bit, 500 ksps with one S&H

- Up to 36 analog inputs

• Flexible and Independent ADC Trigger Sources

• Up to Four Op Amp/Comparators with Direct

Connection to the ADC module:

- Additional dedicated comparator and

7-bit Digital-to-Analog Converter (DAC)

- Two comparator voltage reference outputs

- Programmable references with 128 voltage

points

- Programmable blanking and filtering

• Charge Time Measurement Unit (CTMU):

- Supports mTouch

®

capacitive touch sensing

- Provides high-resolution time

measurement (1 ns)

- On-chip temperature measurement

- Temperature sensor diode

- Nine sources of edge input triggers (CTED1,

CTED2, OCPWM, TMR1, SYSCLK, OSCLK,

FRC, BFRC and LPRC)

16-Bit, 5V Digital Signal Controllers with

PWM, SENT, Op Amps and Advanced Analog Features

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件