Datasheet 搜索 > 双极性晶体管 > ON Semiconductor(安森美) > DTC124EET1 数据手册 > DTC124EET1 其他数据使用手册 1/13 页

器件3D模型

器件3D模型¥ 0.065

DTC124EET1 其他数据使用手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

双极性晶体管

封装:

SC-75-3

描述:

偏置电阻晶体管NPN硅表面贴装晶体管与单片偏置电阻网络 Bias Resistor Transistor NPN Silicon Surface Mount Transistor with Monolithic Bias Resistor Network

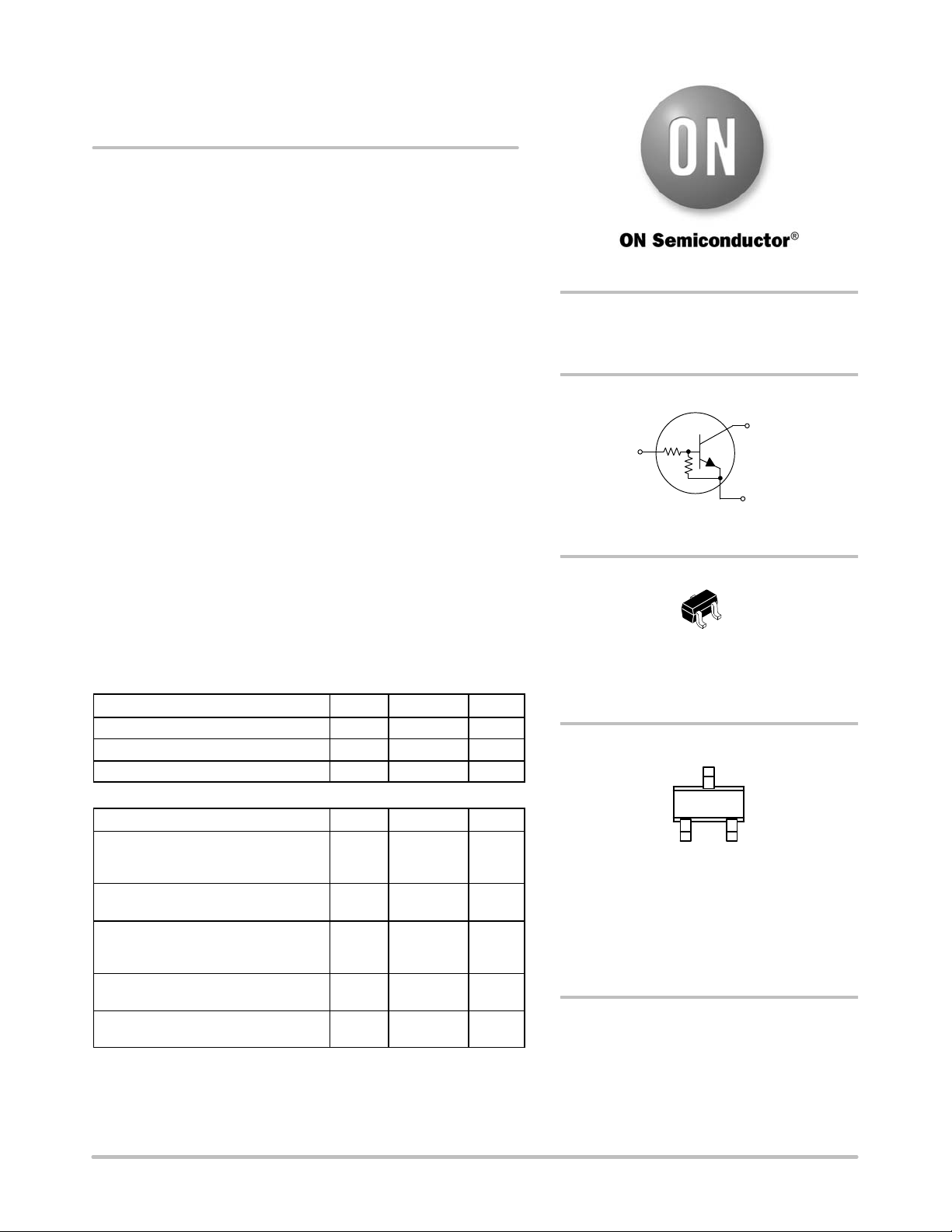

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

典型应用电路图在P12

封装尺寸在P13

焊盘布局在P13

型号编码规则在P1P2P13

标记信息在P1P2

封装信息在P2

技术参数、封装参数在P2

应用领域在P1P12

电气规格在P3P4P5P6P7P8P9P10P11

导航目录

DTC124EET1数据手册

Page:

of 13 Go

若手册格式错乱,请下载阅览PDF原文件

© Semiconductor Components Industries, LLC, 2012

May, 2012 − Rev. 12

1 Publication Order Number:

DTC114EET1/D

DTC114EET1 Series,

SDTC114EET1 Series

Bias Resistor Transistor

NPN Silicon Surface Mount Transistor

with Monolithic Bias Resistor Network

This new series of digital transistors is designed to replace a single

device and its external resistor bias network. The BRT (Bias Resistor

Transistor) contains a single transistor with a monolithic bias network

consisting of two resistors; a series base resistor and a base−emitter

resistor. The BRT eliminates these individual components by

integrating them into a single device. The use of a BRT can reduce

both system cost and board space. The device is housed in the

SC−75/SOT−416 package which is designed for low power surface

mount applications.

Features

• Simplifies Circuit Design

• Reduces Board Space

• Reduces Component Count

• The SC−75/SOT−416 Package Can be Soldered Using Wave or

Reflow

• The Modified Gull−Winged Leads Absorb Thermal Stress During

Soldering Eliminating the Possibility of Damage to the Die

• Pb−Free Packages are Available

• S Prefix for Automotive and Other Applications Requiring Unique

Site and Control Change Requirements; AEC−Q101 Qualified and

PPAP Capable

MAXIMUM RATINGS (T

A

= 25°C unless otherwise noted)

Rating Symbol Value Unit

Collector-Base Voltage V

CBO

50 Vdc

Collector-Emitter Voltage V

CEO

50 Vdc

Collector Current I

C

100 mAdc

THERMAL CHARACTERISTICS

Rating Symbol Value Unit

Total Device Dissipation,

FR−4 Board (Note 1) @ T

A

= 25°C

Derate above 25°C

P

D

200

1.6

mW

mW/°C

Thermal Resistance,

Junction−to−Ambient (Note 1)

R

q

JA

600 °C/W

Total Device Dissipation,

FR−4 Board (Note 2) @ T

A

= 25°C

Derate above 25°C

P

D

300

2.4

mW

mW/°C

Thermal Resistance,

Junction−to−Ambient (Note 2)

R

q

JA

400 °C/W

Junction and Storage Temperature

Range

T

J

, T

stg

−55 to +150 °C

Stresses exceeding Maximum Ratings may damage the device. Maximum

Ratings are stress ratings only. Functional operation above the Recommended

Operating Conditions is not implied. Extended exposure to stresses above the

Recommended Operating Conditions may affect device reliability.

1. FR−4 @ Minimum Pad

2. FR−4 @ 1.0 × 1.0 Inch Pad

NPN SILICON

BIAS RESISTOR TRANSISTORS

PIN 3

COLLECTOR

(OUTPUT)

PIN 2

EMITTER

(GROUND)

PIN 1

BASE

(INPUT)

R1

R2

See detailed ordering, marking, and shipping information in

the package dimensions section on page 2 of this data sheet.

ORDERING INFORMATION

http://onsemi.com

SC−75 (SOT−416)

CASE 463

STYLE 1

3

2

1

MARKING DIAGRAM

xx M G

G

xx = Specific Device Code

xx = (Refer to page 2)

M = Date Code*

G =Pb−Free Package

(Note: Microdot may be in either location)

*Date Code orientation may vary depending

upon manufacturing location.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件