Datasheet 搜索 > 接口芯片 > Micrel(迈瑞) > KSZ8081RNACA TR 数据手册 > KSZ8081RNACA TR 其他数据使用手册 1/49 页

器件3D模型

器件3D模型¥ 6.414

KSZ8081RNACA TR 其他数据使用手册 - Micrel(迈瑞)

制造商:

Micrel(迈瑞)

分类:

接口芯片

封装:

QFN-24

描述:

MICREL SEMICONDUCTOR KSZ8081RNACA TR 以太网控制器, 100 Mbps, IEEE 802.3, 3.135 V, 3.465 V, QFN, 24 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

KSZ8081RNACA TR数据手册

Page:

of 49 Go

若手册格式错乱,请下载阅览PDF原文件

KSZ8081RNA/KSZ8081RND

10Base-T/100Base-TX PHY

with RMII Support

Data Sheet Rev. 1.0

LinkMD is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

November 2012

M9999-110512-1.0

General Description

The KSZ8081RNA is a single-supply 10Base-T/100Base-

TX Ethernet physical-layer transceiver for transmission

and reception of data over standard CAT-5 unshielded

twisted pair (UTP) cable.

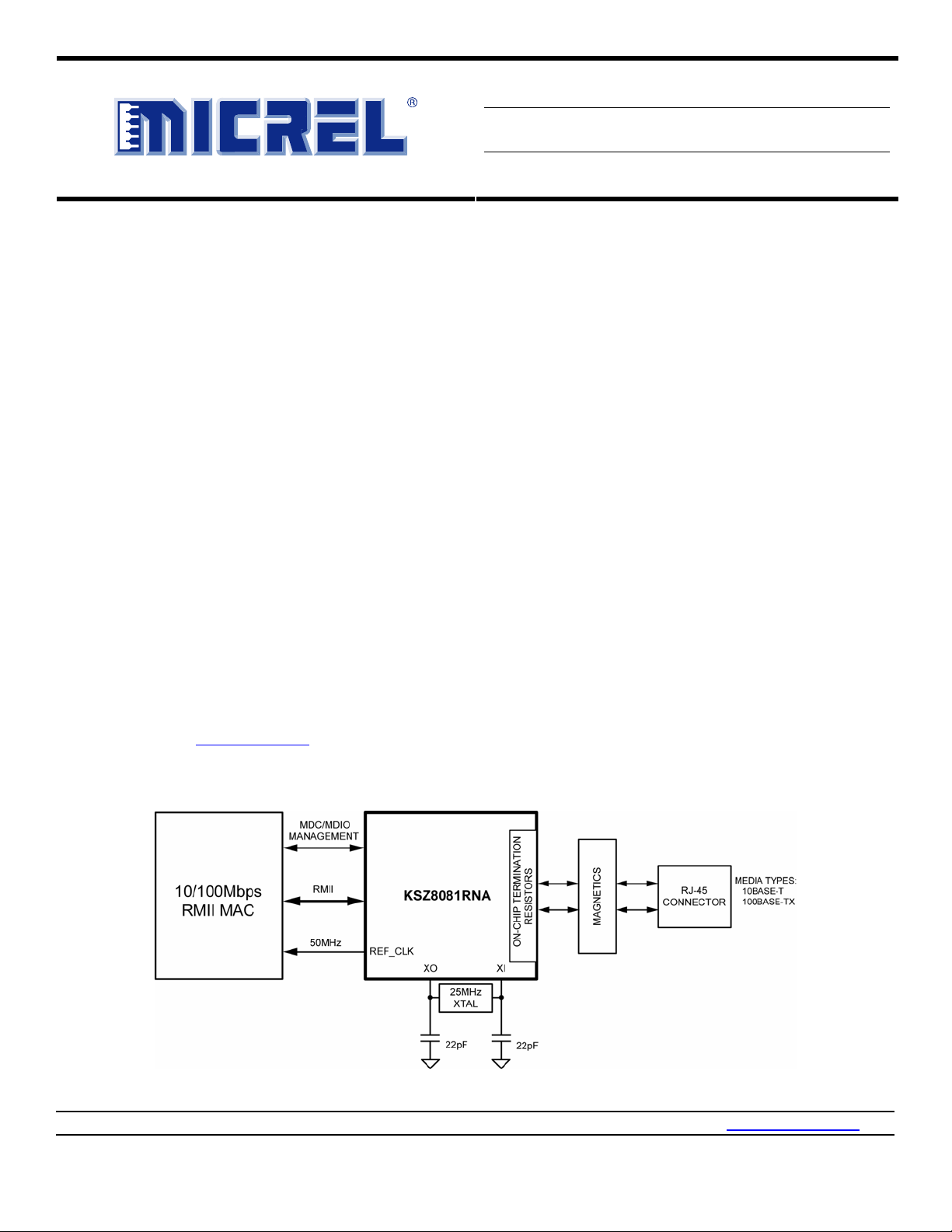

The KSZ8081RNA is a highly-integrated PHY solution. It

reduces board cost and simplifies board layout by using on-

chip termination resistors for the differential pairs and by

integrating a low-noise regulator to supply the 1.2V core, and

by offering 1.8/2.5/3.3V digital I/O interface support.

The KSZ8081RNA offers the Reduced Media Independent

Interface (RMII) for direct connection to RMII-compliant

MACs in Ethernet processors and switches.

As the power-up default, the KSZ8081RNA uses a 25MHz

crystal to generate all required clocks, including the

50MHz RMII reference clock output for the MAC. The

KSZ8081RND is the version that takes in the 50MHz RMII

reference clock as the power-up default.

To facilitate system bring-up and debugging in production

testing and in product deployment, parametric NAND tree

support enables fault detection between KSZ8081RNA

I/Os and the board. Micrel’s LinkMD

®

TDR-based cable

diagnostics identify faulty copper cabling.

The KSZ8081RNA and KSZ8081RND are available in 24-

pin, lead-free QFN packages (see “Ordering Information”)

.

Data sheets and support documentation are available on

Micrel’s web site at: www.micrel.com

.

Features

Single-chip 10Base-T/100Base-TX IEEE 802.3

compliant Ethernet transceiver

RMII v1.2 Interface support with a 50MHz reference

clock output to MAC, and an option to input a 50MHz

reference clock

RMII back-to-back mode support for a 100Mbps copper

repeater

MDC/MDIO management interface for PHY register

configuration

Programmable interrupt output

LED outputs for link and activity status indication

On-chip termination resistors for the differential pairs

Baseline wander correction

HP Auto MDI/MDI-X to reliably detect and correct

straight-through and crossover cable connections with

disable and enable option

Auto-negotiation to automatically select the highest link-

up speed (10/100Mbps) and duplex (half/full)

Power-down and power-saving modes

LinkMD TDR-based cable diagnostics to identify faulty

copper cabling

Parametric NAND Tree support for fault detection

between chip I/Os and the board

Functional Diagram

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件