Datasheet 搜索 > 逻辑芯片 > ON Semiconductor(安森美) > MC14070BCP 数据手册 > MC14070BCP 其他数据使用手册 1/8 页

器件3D模型

器件3D模型¥ 4.21

MC14070BCP 其他数据使用手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

逻辑芯片

封装:

DIP-14

描述:

SSI CMOS四路异或和NOR门 CMOS SSI Quad Exclusive OR and NOR Gates

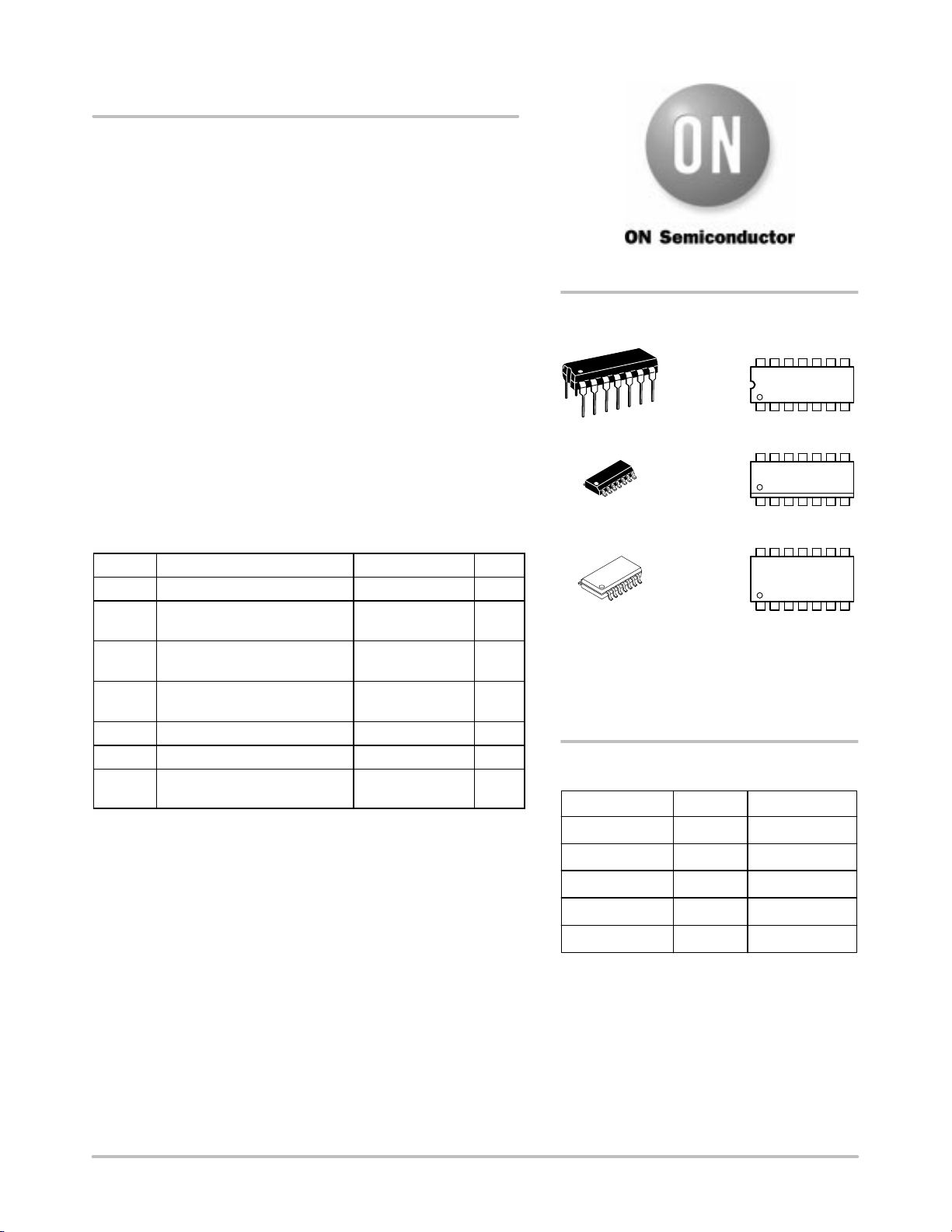

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MC14070BCP数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

Semiconductor Components Industries, LLC, 2000

August, 2000 – Rev. 4

1 Publication Order Number:

MC14070B/D

MC14070B, MC14077B

CMOS SSI

Quad Exclusive “OR” and “NOR” Gates

The MC14070B quad exclusive OR gate and the MC14077B quad

exclusive NOR gate are constructed with MOS P–channel and

N–channel enhancement mode devices in a single monolithic

structure. These complementary MOS logic gates find primary use

where low power dissipation and/or high noise immunity is desired.

• Supply Voltage Range = 3.0 Vdc to 18 Vdc

• All Outputs Buffered

• Capable of Driving Two Low–Power TTL Loads or One Low–Power

Schottky TTL Load Over the Rated Temperature Range

• Double Diode Protection on All Inputs

• MC14070B — Replacement for CD4030B and CD4070B Types

• MC14077B — Replacement for CD4077B Type

MAXIMUM RATINGS (Voltages Referenced to V

SS

) (Note 2.)

Symbol

Parameter Value Unit

V

DD

DC Supply Voltage Range –0.5 to +18.0 V

V

in

, V

out

Input or Output Voltage Range

(DC or Transient)

–0.5 to V

DD

+ 0.5 V

I

in

, I

out

Input or Output Current

(DC or Transient) per Pin

±10 mA

P

D

Power Dissipation,

per Package (Note 3.)

500 mW

T

A

Ambient Temperature Range –55 to +125 °C

T

stg

Storage Temperature Range –65 to +150 °C

T

L

Lead Temperature

(8–Second Soldering)

260 °C

2. Maximum Ratings are those values beyond which damage to the device

may occur.

3. Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/C From 65C To 125C

This device contains protection circuitry to guard against damage due to high

static voltages or electric fields. However, precautions must be taken to avoid

applications of any voltage higher than maximum rated voltages to this

high–impedance circuit. For proper operation, V

in

and V

out

should be constrained

to the range V

SS

(V

in

or V

out

) V

DD

.

Unused inputs must always be tied to an appropriate logic voltage level (e.g.,

either V

SS

or V

DD

). Unused outputs must be left open.

http://onsemi.com

xx = Specific Device Code

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

Device Package Shipping

ORDERING INFORMATION

MC140XXBCP PDIP–14 2000/Box

MC140XXBD SOIC–14

2750/Box

MC140XXBDR2 SOIC–14 2500/Tape & Reel

MC140XXBF SOEIAJ–14 See Note 1.

MARKING

DIAGRAMS

1

14

PDIP–14

P SUFFIX

CASE 646

MC140xxBCP

AWLYYWW

SOIC–14

D SUFFIX

CASE 751A

1

14

140xxB

AWLYWW

SOEIAJ–14

F SUFFIX

CASE 965

1

14

MC140xxB

ALYW

MC140XXBFEL SOEIAJ–14 See Note 1.

1. For ordering information on the EIAJ version of

the SOIC packages, please contact your local

ON Semiconductor representative.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件