Datasheet 搜索 > 锁存器 > Fairchild(飞兆/仙童) > MM74HC573WM 数据手册 > MM74HC573WM 其他数据使用手册 2/10 页

器件3D模型

器件3D模型¥ 2.794

MM74HC573WM 其他数据使用手册 - Fairchild(飞兆/仙童)

制造商:

Fairchild(飞兆/仙童)

分类:

锁存器

封装:

SOIC-20

描述:

FAIRCHILD SEMICONDUCTOR MM74HC573WM 芯片, 74HC CMOS逻辑器件

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MM74HC573WM数据手册

Page:

of 10 Go

若手册格式错乱,请下载阅览PDF原文件

© 2005 Fairchild Semiconductor Corporation DS005212 www.fairchildsemi.com

September 1983

Revised May 2005

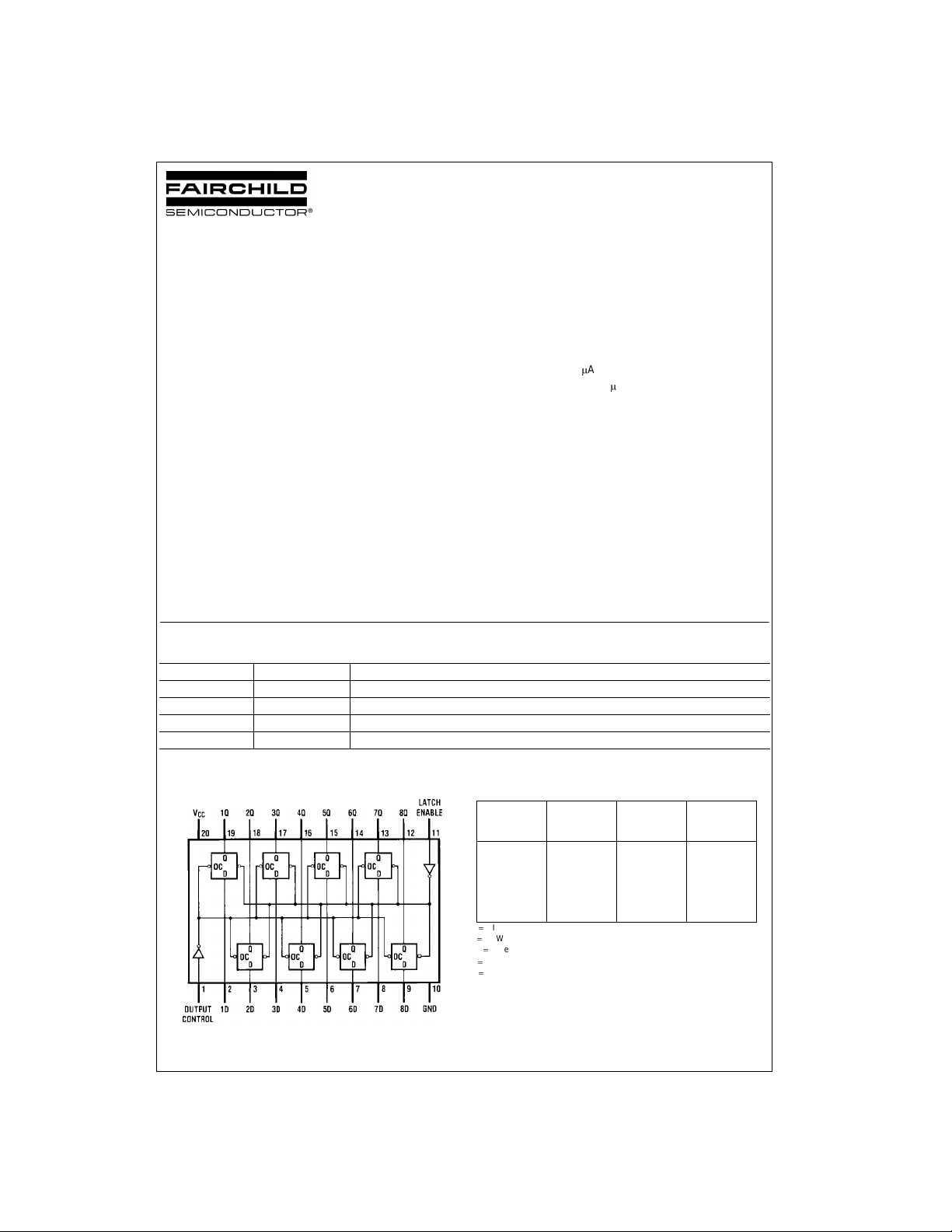

MM74HC573 3-STATE Octal D-Type Latch

MM74HC573

3-STATE Octal D-Type Latch

General Description

The MM74HC573 high speed octal D-type latches utilize

advanced silicon-gate P-well CMOS technology. They pos-

sess the high noise immunity and low power consumption

of standard CMOS integrated circuits, as well as the ability

to drive 15 LS-TTL loads. Due to the large output drive

capability and the 3-STATE feature, these devices are ide-

ally suited for interfacing with bus lines in a bus organized

system.

When the LATCH ENABLE(LE) input is HIGH, the Q out-

puts will follow the D inputs. When the LATCH ENABLE

goes LOW, data at the D inputs will be retained at the out-

puts until LATCH ENABLE returns HIGH again. When a

HIGH logic level is applied to the OUTPUT CONTROL OC

input, all outputs go to a HIGH impedance state, regardless

of what signals are present at the other inputs and the state

of the storage elements.

The 74HC logic family is speed, function and pinout com-

patible with the standard 74LS logic family. All inputs are

protected from damage due to static discharge by internal

diode clamps to V

CC

and ground.

Features

■ Typical propagation delay: 18 ns

■ Wide operating voltage range: 2 to 6 volts

■ Low input current: 1

P

A maximum

■ Low quiescent current: 80

P

A maximum (74HC Series)

■ Compatible with bus-oriented systems

■ Output drive capability: 15 LS-TTL loads

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Connection Diagram

Top View

Truth Table

H

HIGH Level

L

LOW Level

Q

0

Level of output before steady-state input conditions were established.

Z

High Impedance

X

Don't Care

Order Number Package Number Package Description

MM74HC573WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide

MM74HC573SJ M20D 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

MM74HC573MTC MTC20 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

MM74HC573N N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Output Latch Data Output

Control Enable

LHHH

LHLL

LLXQ

0

HXXZ

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件