Datasheet 搜索 > MOS管 > ON Semiconductor(安森美) > NDS7002A 数据手册 > NDS7002A 产品设计图 1/2 页

¥ 0.18

NDS7002A 产品设计图 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

MOS管

封装:

SOT-23-3

描述:

增强模式 N 通道 MOSFET, Fairchild Semiconductor增强模式场效应晶体管 (FET) 使用了 Fairchild 的专利高单元密度的 DMOS 技术进行生产。 这种高密度工艺设计用于尽量减小通态电阻,提供耐用可靠的性能和快速切换。### MOSFET 晶体管,Fairchild SemiconductorFairchild 提供大量 MOSFET 设备组合,包括高电压 (>250V) 低电压 (<250V) 类型。 先进的硅技术提供更小的芯片尺寸,其整合到多种工业标准和耐热增强型封装中。 Fairchild MOSFET 通过降低电压峰值和过冲提供极佳的设计可靠性,以减少结电容和反向恢复电荷,无需额外外部元件即可保持系统启动和运行更长时间。

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装尺寸在P1

焊盘布局在P1

标记信息在P1P2

导航目录

NDS7002A数据手册

Page:

of 2 Go

若手册格式错乱,请下载阅览PDF原文件

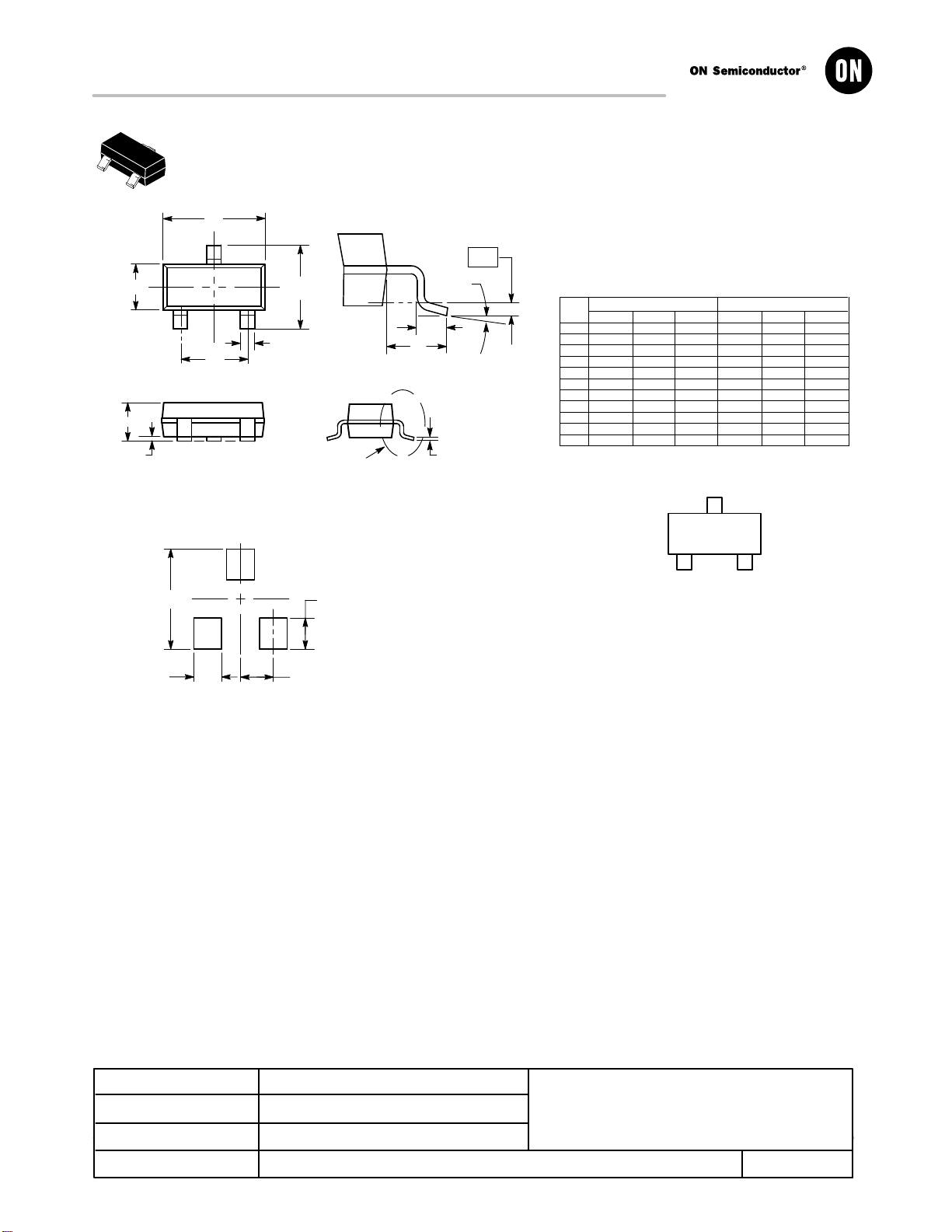

SOT−23 (TO−236)

CASE 318−08

ISSUE AR

DATE 10 OCT 201

6

SCALE 4:1

D

A1

3

1

2

1

XXXMG

G

XXX = Specific Device Code

M = Date Code

G = Pb−Free Package

*This information is generic. Please refer to

device data sheet for actual part marking.

Pb−Free indicator, “G” or microdot “ G”,

may or may not be present.

GENERIC

MARKING DIAGRAM*

NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH.

MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF

THE BASE MATERIAL.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH,

PROTRUSIONS, OR GATE BURRS.

SOLDERING FOOTPRINT

VIEW C

L

0.25

L1

e

E

E

b

A

SEE VIEW C

DIM

A

MIN NOM MAX MIN

MILLIMETERS

0.89 1.00 1.11 0.035

INCHES

A1 0.01 0.06 0.10 0.000

b 0.37 0.44 0.50 0.015

c 0.08 0.14 0.20 0.003

D 2.80 2.90 3.04 0.110

E 1.20 1.30 1.40 0.047

e 1.78 1.90 2.04 0.070

L 0.30 0.43 0.55 0.012

0.039 0.044

0.002 0.004

0.017 0.020

0.006 0.008

0.114 0.120

0.051 0.055

0.075 0.080

0.017 0.022

NOM MAX

L1

H

STYLE 22:

PIN 1. RETURN

2. OUTPUT

3. INPUT

STYLE 6:

PIN 1. BASE

2. EMITTER

3. COLLECTOR

STYLE 7:

PIN 1. EMITTER

2. BASE

3. COLLECTOR

STYLE 8:

PIN 1. ANODE

2. NO CONNECTION

3. CATHODE

STYLE 9:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 10:

PIN 1. DRAIN

2. SOURCE

3. GATE

STYLE 11:

PIN 1. ANODE

2. CATHODE

3. CATHODE−ANODE

STYLE 12:

PIN 1. CATHODE

2. CATHODE

3. ANODE

STYLE 13:

PIN 1. SOURCE

2. DRAIN

3. GATE

STYLE 14:

PIN 1. CATHODE

2. GATE

3. ANODE

STYLE 15:

PIN 1. GATE

2. CATHODE

3. ANODE

STYLE 16:

PIN 1. ANODE

2. CATHODE

3. CATHODE

STYLE 17:

PIN 1. NO CONNECTION

2. ANODE

3. CATHODE

STYLE 18:

PIN 1. NO CONNECTION

2. CATHODE

3. ANODE

STYLE 19:

PIN 1. CATHODE

2. ANODE

3. CATHODE−ANODE

STYLE 23:

PIN 1. ANODE

2. ANODE

3. CATHODE

STYLE 20:

PIN 1. CATHODE

2. ANODE

3. GATE

STYLE 21:

PIN 1. GATE

2. SOURCE

3. DRAIN

STYLE 1 THRU 5:

CANCELLED

STYLE 24:

PIN 1. GATE

2. DRAIN

3. SOURCE

STYLE 25:

PIN 1. ANODE

2. CATHODE

3. GATE

STYLE 26:

PIN 1. CATHODE

2. ANODE

3. NO CONNECTIO

N

STYLE 27:

PIN 1. CATHODE

2. CATHODE

3. CATHODE

2.10 2.40 2.64 0.083 0.094 0.104

H

E

0.35 0.54 0.69 0.014 0.021 0.027

c

0 −−− 10 0 −−− 10

T

°°°°

(Note: Microdot may be in either location)

T

3X

TOP VIEW

SIDE VIEW

END VIEW

2.90

0.80

DIMENSIONS: MILLIMETERS

0.90

PITCH

3X

3X

0.95

RECOMMENDED

MECHANICAL CASE OUTLINE

PACKAGE DIMENSIONS

http://onsemi.com

1

© Semiconductor Components Industries, LLC, 2002

October, 2002 − Rev. 0

Case Outline Number:

XXX

DOCUMENT NUMBER:

STATUS:

NEW STANDARD:

DESCRIPTION:

98ASB42226B

ON SEMICONDUCTOR STANDARD

SOT−23 (TO−236)

Electronic versions are uncontrolled except when

accessed directly from the Document Repository. Printed

versions are uncontrolled except when stamped

“CONTROLLED COPY” in red.

PAGE 1 OF 2

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件