Datasheet 搜索 > Freescale(飞思卡尔) > P4080NXN1NNB 数据手册 > P4080NXN1NNB 其他数据使用手册 1/3 页

¥ 0

P4080NXN1NNB 其他数据使用手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

P4080NXN1NNB数据手册

Page:

of 3 Go

若手册格式错乱,请下载阅览PDF原文件

Freescale QorIQ™ communications platforms

are the next-generation evolution of our

leading PowerQUICC

®

communications

processors. Built using high-performance

Power Architecture

®

cores, QorIQ platforms

enable a new era of networking innovation

where the reliability, security and quality of

service for every connection matters.

QorIQ P4080 Multicore Processor

The QorIQ P4080 multicore processor, the

first product offered in the QorIQ P4 platform

series, delivers industry-leading performance

in the under 30-watt power category.

It combines eight Power Architecture e500mc

cores operating at frequencies up to

1.5 GHz with high-performance datapath

acceleration logic, as well as networking

I/O and other peripheral bus interfaces.

The P4080, built in 45 nm technology, is

designed to deliver high-performance,

next-generation networking services in a

very low power envelope.

The QorIQ P4080 processor is designed for

combined control and dataplane processing,

enabling high-performance layers 2–7

processing. Its high level of integration offers

significant performance benefits compared to

multiple discrete devices, while also greatly

simplifying board design. The processor is

well-suited for applications that are highly

compute-intensive, I/O-intensive or both.

This makes it ideal for applications such

as enterprise and service provider routers,

switches, media gateways, base station

controllers, radio network controllers (RNCs),

access gateways for Long Term Evolution (LTE)

and general-purpose embedded computing

systems in the networking, telecom, industrial,

aerospace and defense markets.

Key Features

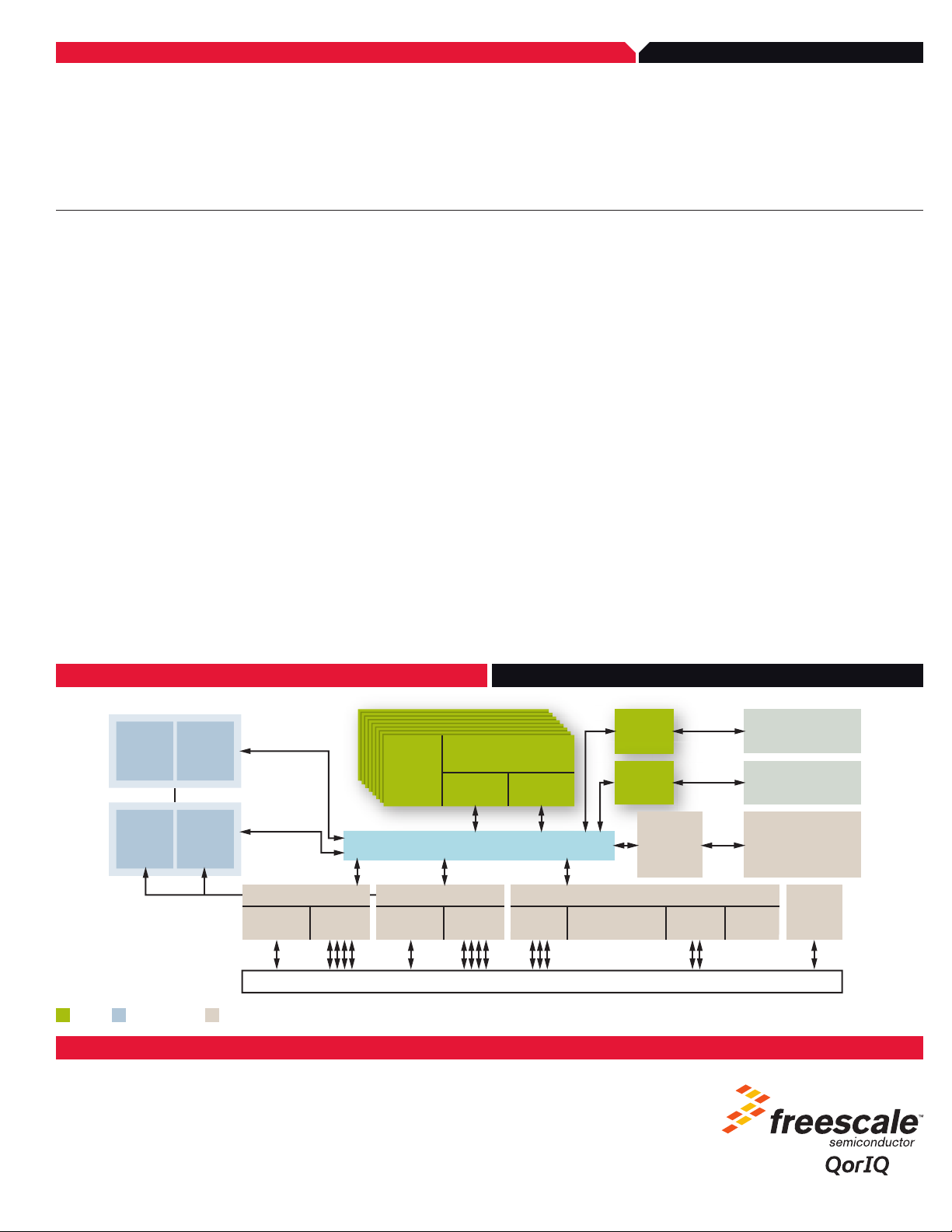

Freescale delivers a groundbreaking three-

tiered cache hierarchy on the QorIQ P4

platform. Each core has an integrated Level 1

(L1) cache as well as a dedicated Level 2 (L2)

backside cache that can significantly improve

performance. Finally, a multi-megabyte Level

3 (L3) cache is also provided for those tasks

for which a shared cache is desirable.

The CoreNet™ coherency fabric is a key

design component of the QorIQ P4 platform.

It manages full coherency of the caches and

provides scalable on-chip, point-to-point

connectivity supporting concurrent traffic to

and from multiple resources connected to the

fabric, eliminating single-point bottlenecks

for non-competing resources. This eliminates

bus contention and latency issues associated

with scaling shared bus/shared memory

architectures that are common in other

multicore approaches.

QorIQ™ Communications Platforms

P4 Series

P4080 multicore processor

Buffer

Manager

Queue

Manager

Core Acceleration Interface

DDR2/DDR3

SDRAM Controller

DDR2/DDR3

SDRAM Controller

2 x DUART, 4 x I

2

C,

Interrupt Control,

GPIO, SD/MMC, SPI,

2 x USB 2.0/ULPI

Encryption

RegEx

Pattern

Matching

Engine

Enhanced

Local Bus

Controller

(eLBC)

128 KB

Backside

L2 Cache

32 KB

L1 I-Cache

Power Architecture

®

e500mc Core

32 KB

L1 D-Cache

CoreNet™ Coherency Fabric

2 x 4-ch.

DMA

2 x 4-ch.

DMA

3 x PCI

Express

®

On-Chip NetworkOn-Chip Network

2 x Serial

RapidIO

®

18-lane SerDes

RapidIO Message

Unit (RMU)

Frame Manager

4 x 1 Gbps

Ethernet

1 x 10 Gbps

Ethernet

Real-Time

Debug

Frame Manager

4 x 1 Gbps

Ethernet

1 x 10 Gbps

Ethernet

QorIQ™ P4080 Block Diagram

1024 KB

Frontside

L3 Cache

1024 KB

Frontside

L3 Cache

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件