Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC16F1526-I/PT 数据手册 > PIC16F1526-I/PT 其他数据使用手册 4/9 页

器件3D模型

器件3D模型¥ 25.826

PIC16F1526-I/PT 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-64

描述:

MICROCHIP PIC16F1526-I/PT 微控制器, 8位, 闪存, AEC-Q100, PIC16F152x, 20 MHz, 14 KB, 768 Byte, 64 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

PIC16F1526-I/PT数据手册

Page:

of 9 Go

若手册格式错乱,请下载阅览PDF原文件

PIC16(L)F1526/1527

DS80000520E-page 4 2011-2014 Microchip Technology Inc.

4. Module: Oscillator

4.1 OSCSTAT bits: HFIOFR and HFIOFS

When HFINTOSC is selected, the HFIOFR and

the HFIOFS bits will become set when the

oscillator becomes ready and stable. Once these

bits are set, they become “stuck”, indicating that

HFINTOSC is always ready and stable. If the

HFINTOSC is disabled, the bits fail to be cleared.

Work around

None.

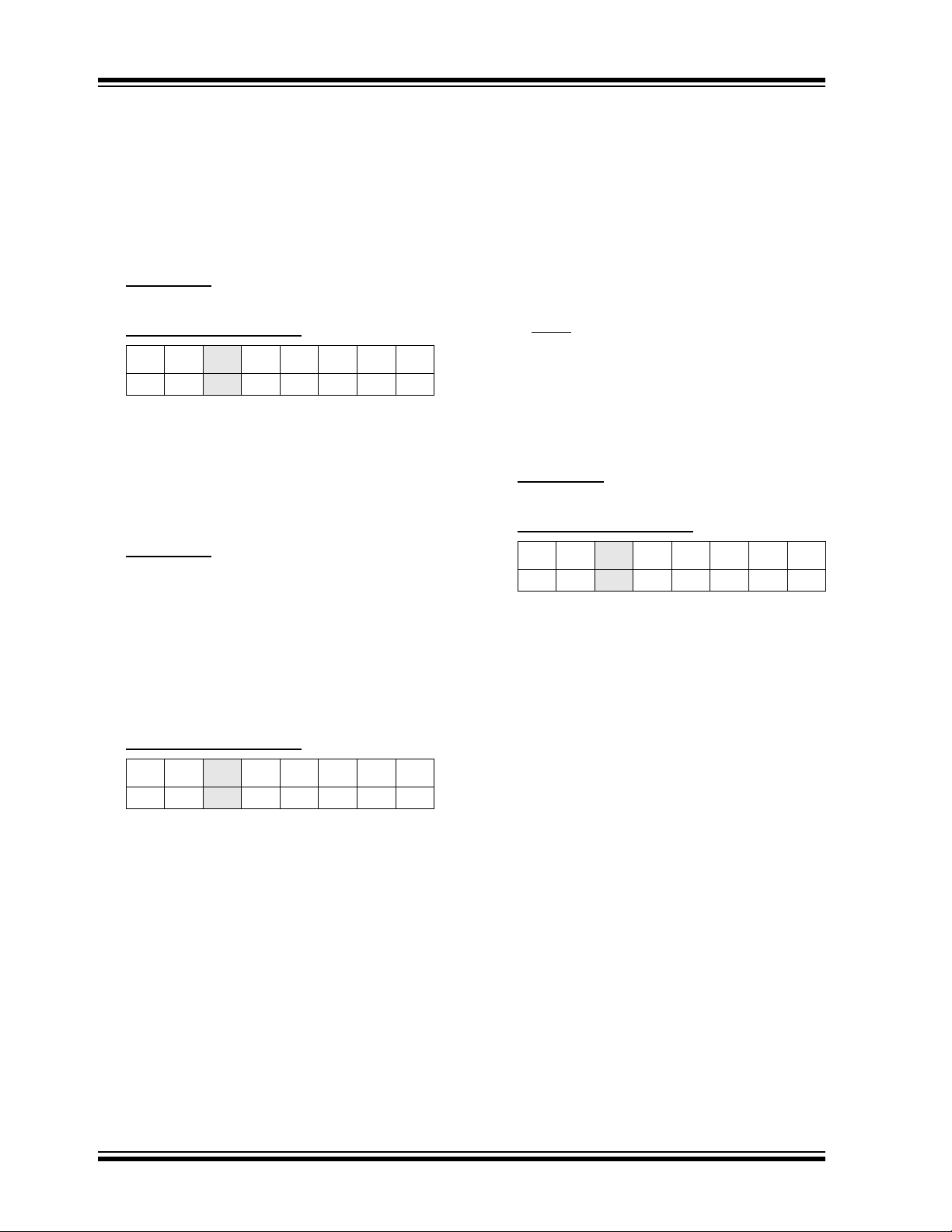

Affected Silicon Revisions

4.2 Clock Switching

When switching clock sources between INTOSC

clock source and an external clock source, one

corrupted instruction may be executed after the

switch occurs.

This issue does not affect the Two-Speed start-up

or the Fail-Safe Clock Monitor operation.

Work around

When switching from an external oscillator clock

source, first switch to 16 MHz HFINTOSC. Once

running at 16 MHz HFINTOSC, configure IRCF to

run at desired internal oscillator frequency.

When switching from an internal oscillator

(INTOSC) to an external oscillator clock source,

first switch to HFINTOSC High-Power mode (8

MHz or 16 MHz). Once running from HFINTOSC,

switch to the external oscillator clock source.

Affected Silicon Revisions

4.3 Oscillator Start-up Timer (OST) bit

During the Two-Speed Start-up sequence, the

OST is enabled to count 1024 clock cycles. After

the count is reached, the OSTS bit is set, and the

system clock is held low until the next falling edge

of the external crystal (LP, XT or HS mode), before

switching to the external clock source.

When an external oscillator is configured as

primary clock and Fail-Safe Clock mode is enabled

(FCMEN = 1), any of the following conditions will

result in the Oscillator Start-up Timer (OST) failing

to restart:

•MCLR

Reset

• Wake from Sleep

• Clock change from INTOSC to Primary Clock

This anomaly will manifest itself as a clock failure

condition for external oscillators, which takes

longer than the clock failure time-out period to

start.

Work around

None.

Affected Silicon Revisions

A2 A3 A5

XX

A2 A3 A5

XX

X

A2 A3 A5

XX

X

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件