Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC16F1788T-I/SO 数据手册 > PIC16F1788T-I/SO 其他数据使用手册 3/8 页

器件3D模型

器件3D模型¥ 14.022

PIC16F1788T-I/SO 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

SOIC-28

描述:

8位微控制器 -MCU 28KB Flash, 2KB RAM 256B EEPROM

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

PIC16F1788T-I/SO数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

2013 Microchip Technology Inc. DS80000575B-page 3

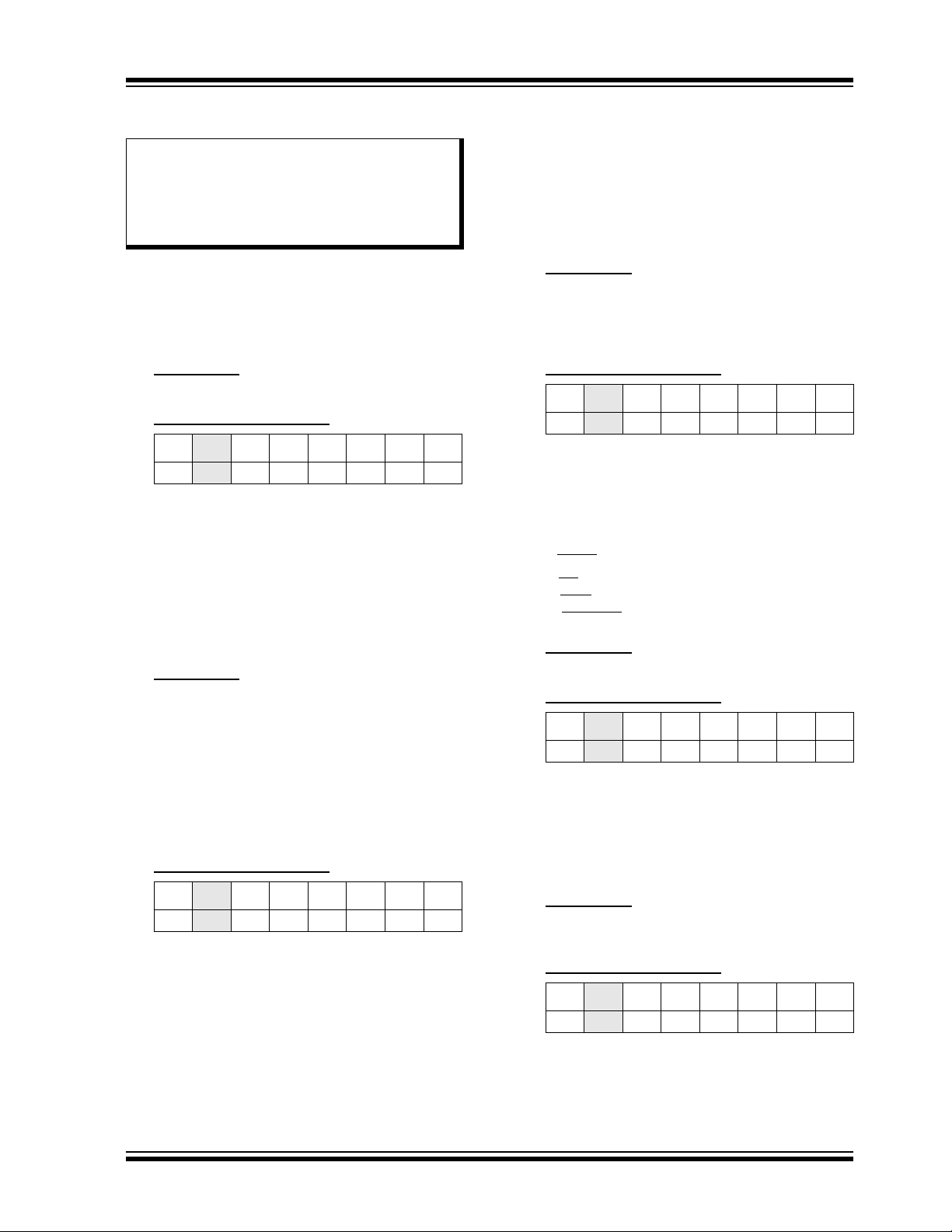

PIC16(L)F1788/1789

Silicon Errata Issues

1. Module: Comparator

1.1 No Low-Power, No Low-Speed Mode

The comparator operation in Low-Power, Low-

Speed mode (CxSP = 0) may not perform properly.

Work around

Use the comparator in High-Power mode.

Affected Silicon Revisions

2. Module: PSMC

2.1 Rising Edge Inhibit

When the period and falling edge sources are from

the same asynchronous input, then a race

condition may occur where the period is detected

before the falling edge. When this occurs, the

falling edge properly terminates the cycle but

subsequent rising edge inputs are ignored.

Work around

To configure the PSMC for fixed off-time and

variable frequency, set the following:

• Period = Asynchronous feedback

• Rising Event = Synchronous @

PSMCxPH = 0

• Falling Event = Synchronous @

PSMCxDC = Off Time

• Output inverted so drive time is from falling

event to period event.

Affected Silicon Revisions

2.2 64 MHz Clock

When the Configuration bits select both PLL

enabled and INTOSC as the default system clock,

then the 64 MHz PSMC clock will not operate after

a device Reset until the IRCF<3:0> bits of the

OSCCON register are set to '111x'. The IRCF bits

can then be set to any desired value and the

64 MHz clock will continue to operate.

Work around

Ensure that the PLLEN bit of the CONFIG2

register is cleared when the FOSC<2:0> bits of the

CONFIG1 register select the INTOSC

(FOSC<2:0> = 100).

Affected Silicon Revisions

3. Module: Resets

3.1 Low-Power Sleep (PIC16F1788/1789 devices

only)

When the device is in Low-Power Sleep

(VREGPM = 1 and SLEEP instruction is executed),

a MCLR

Reset will be reported as a POR Reset:

•PD

= 1

•POR

= 0

• RDMCLR

= 1

Work around

Use Normal-Power Sleep mode (VREGPM = 0).

Affected Silicon Revisions

4. Module: CPU

4.1 BRA/BRW

If a BRA or BRW instruction is executed

concurrently with an interrupt event, the ISR

routine can restore the PC to an incorrect value.

Work around

Use the GOTO instruction rather than the BRA or

BRW instruction.

Affected Silicon Revisions

Note: This document summarizes all silicon

errata issues from all revisions of silicon,

previous as well as current. Only the

issues indicated by the shaded column in

the following tables apply to the current

silicon revision (B1).

B0

B1

X

X

B0

B1

X

X

B0 B1

X

X

B0

B1

X

X

B0 B1

X

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件