Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC16F18323-I/SL 数据手册 > PIC16F18323-I/SL 其他数据使用手册 5/442 页

器件3D模型

器件3D模型¥ 6.585

PIC16F18323-I/SL 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

SOIC-14

描述:

PIC16F18313/18323 8 位微控制器Microchip PIC16F 系列是 8 位 MCU,包含 Microchip PIC® 体系结构,提供各种引脚和封装选项。 PIC16F18313/18323 微控制器基于 Microchip 增强型中级芯,且包括全新的低功率功能。 随外围模块禁用功能一起,还增加了 IDLE 和 DOZE 模式,允许从电源导轨和时钟树移除外围设备,实现零功率泄漏。### 微控制器功能最大 32 MHz CPU 速度 49 个指令 16 级硬件堆栈 中断功能 内部振荡器 6 或 12 个输入/输出引脚 通电重置 (POR) 可配置开机计时器 (PWRTE) 掉电重置 (BOR) 和低功耗掉电重置 (LPBOR) 窗口监控计时器 (WWDT) 在线串行编程 (ICSP) 在线调试 (ICD) 低电压编程 (LVP) 外设引脚选择 (PPS) ### 省电功能外围模块禁用 ( PMD ) - 可禁用不使用的外围设备,确保最小功耗 睡眠、待机和小憩低功率模式 睡眠模式:50 nA @ 1.8 V(典型) 监控计时器:500 nA @ 1.8 V(典型) 次级振荡器:500 nA @ 32 kHz 工作电流:8 μA @ 32 kHz 1.8 V(典型) ### 外围功能10 位模拟到数字转换器 - 5 或 11 通道,具体取决于型号 5 位数字到模拟转换器 (DAC) 两个比较器 (COMP) - 1 或 2,具体取决于型号 电压参考 两个可配置逻辑电池 (CLC) 补充波形发生器 (CWG) 两个采集/比较/PWM (CCP) 模块 两个 10 位 PWM 数字控制振荡器 (NCO) 与 EUSART – RS-232、RS-485 和 LIN 兼容 主同步串行端口 (MSSP) – I2C、SMBus、PMBus 兼容 数据信号调制器 (DSM) 两个 8 位计时器,带硬件限制计时器 (HLT) 一个 16 位计时器 ### PIC16 微控制器展开

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P4P11P12P13P14P15P148P273P364P365Hot

典型应用电路图在P155P365

原理图在P10P16P56P65P73P105P138P149P153P158P160P167

封装尺寸在P419

标记信息在P415P416P417P418

封装信息在P415P419P420P421P422P424P425P426P428P429P431P432

技术参数、封装参数在P68P85P102P160P161P388P394P395P397P398P400

应用领域在P54

电气规格在P85P102

导航目录

PIC16F18323-I/SL数据手册

Page:

of 442 Go

若手册格式错乱,请下载阅览PDF原文件

2015 Microchip Technology Inc. Preliminary DS40001799A-page 5

PIC16(L)F18313/18323

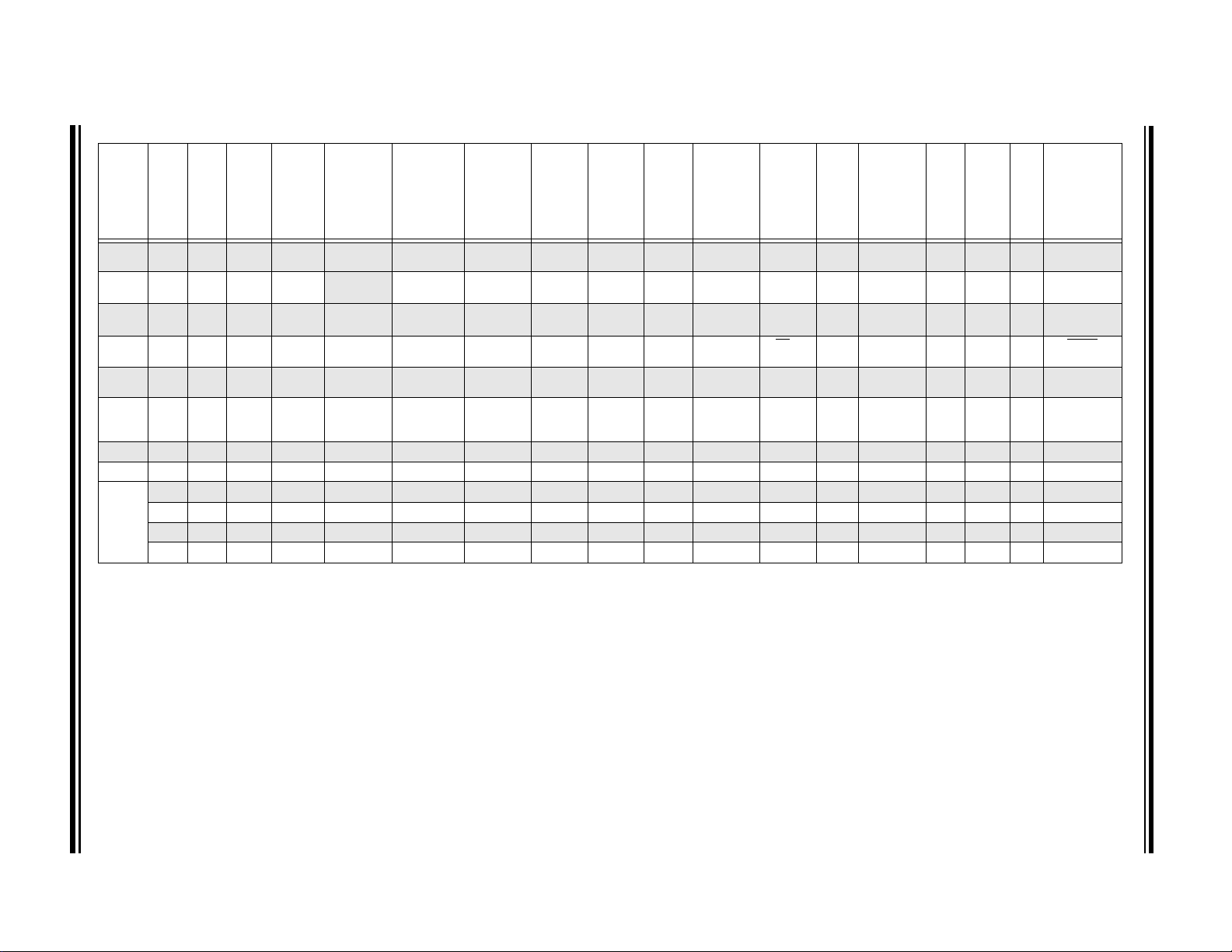

TABLE 1: 8-PIN ALLOCATION TABLE (PIC16(L)F18313)

I/O

(2)

PDIP/SOIC/UDFN

ADC

Reference

Comparator

NCO

DAC

DSM

Timers

CCP

PWM

CWG

MSSP

EUSART

CLC

CLKR

Interrupt

Pull-up

Basic

RA0 7 ANA0 — C1IN0+ — DAC1OUT MDCIN1

(1)

— — — — — — CLCIN3

(1)

— IOC Y ICDDAT/

ICSPDAT

RA1 ANA1 VREF+

C1IN0-

—

DAC1

REF+MDMIN

(1)

————

SCK

(1)

SCL

(1,3,4)

RX

(1))

DT

(1,3)

CLCIN2

(1)

—

IOC Y ICDCLK/

ICSPCLK

RA2 5 ANA2 VREF- — — DAC1REF- — T0CKI

(1)

— — CWG1IN

(1)

SDA

(1,3,4)

SDI

(1)

— — — INT

(1)

IOC

Y —

RA3 4

—— — — — — — — — —

SS

(1)

—

CLCIN0

(1)

—

IOC Y MCLR

VPP

RA4 3 ANA4

— C1IN1- — — —

T1G

(1)

SOSCO

— — — — — — —

IOC Y CLKOUT

OSC2

RA5 2 ANA5

—— — —

MDCIN2

(1)

T1CKI

(1)

SOSCIN

SOSCI

CCP1

(1)

CCP2

(1)

—— ——

CLCIN1

(1)

—

IOC Y CLKIN

OSC1

VDD 1

— — — — — — — — — — — — —

—

— —

VDD

VSS 8

—— — — — — — — — — — — — ———

VSS

OUT

(2)

— — — C1OUT NCO — DSM TMR0 CCP1 PWM5 CWG1A SDA

(3)

CK CLC1OUT CLKR — — —

—— — — — — — —

CCP2 PWM6 CWG1B SCL

(3)

DT

(3)

CLC2OUT

——— —

— — — — — — — — — — CWG1C SDO TX — — — — —

—— — — — — — — — —

CWG1D SCK

————— —

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 12-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 12-2.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I

2

C™ logic levels as described in Section 12.3 “Bidirectional Pins”; clock and data signals may be assigned to any of these pins. Assignments to the other pins (e.g.,

RA5) will operate, but logic levels will be standard TTL/ST as selected by the INLVL register.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件