Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F45J10-EPT 数据手册 > PIC18F45J10-EPT 其他数据使用手册 1/6 页

器件3D模型

器件3D模型¥ 0

PIC18F45J10-EPT 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

PIC18F45J10-EPT数据手册

Page:

of 6 Go

若手册格式错乱,请下载阅览PDF原文件

© 2006 Microchip Technology Inc. DS80269B-page 1

PIC18F24J10/25J10/44J10/45J10

The PIC18F24J10/25J10/44J10/45J10 Rev. A2 parts

you have received conform functionally to the Device

Data Sheet (DS39682A), except for the anomalies

described below. Any Data Sheet Clarification issues

related to the PIC18F24J10/25J10/44J10/45J10 will be

reported in a separate Data Sheet errata. Please check

the Microchip web site for any existing issues.

The following silicon errata apply only to

PIC18F24J10/25J10/44J10/45J10 devices with these

Device/Revision IDs:

1. Module: Timer1

In 16-Bit Asynchronous Counter mode or 16-Bit

Asynchronous Oscillator mode, the TMR1H buffer

does not update when TMR1L is read. This issue

only affects reading the TMR1H registers. The tim-

ers increment and set the interrupt flags as

expected. The Timer registers can also be written

as expected.

Work around

Use 8-bit mode by clearing the RD16 (T1CON<7>)

bit or use the synchronization option by clearing

T1SYNC

(T1CON<2>).

2. Module: EUSART

In asynchronous duplex communication, the

reception can get corrupted if any bit of the TXSTA

register is modified during a reception.

Work around

The CSRC (TXSTA<7>) bit should not be set.

Though this is a “don’t care” bit in Asynchronous

mode, make sure that this bit is not set.

3. Module: EUSART

In Synchronous mode, EUSART baud rates using

SPBRG values of ‘0’ and ‘1’ may not function

correctly.

Work around

Use another baud rate configuration to generate

the desired baud rate.

4. Module: EUSART

After the last received byte has been read from the

EUSART receive buffer, RCREG, the value is no

longer valid for subsequent read operations. The

RCREG register should only be read once for each

byte received.

Work around

After each byte is received from the EUSART,

store the byte into a user variable. To determine

when a byte is available to read from RCREG, poll

the RCIDL (BAUDCON<6>) bit for a low-to-high

transition, or use the EUSART Receive Interrupt

Flag, RCIF (PIR1<5>).

5. Module: EUSART

In 9-Bit Asynchronous, Full-Duplex, Receive

mode, received data may be corrupted if the TX9D

bit (TXSTA<0>) is not modified immediately after

RCIDL (BAUDCON<6>) is set.

Work around

Only write to TX9D when a reception is not in

progress (RCIDL = 1). No interrupt is associated

with RCIDL, therefore, it must be polled in software

to determine when TX9D can be updated.

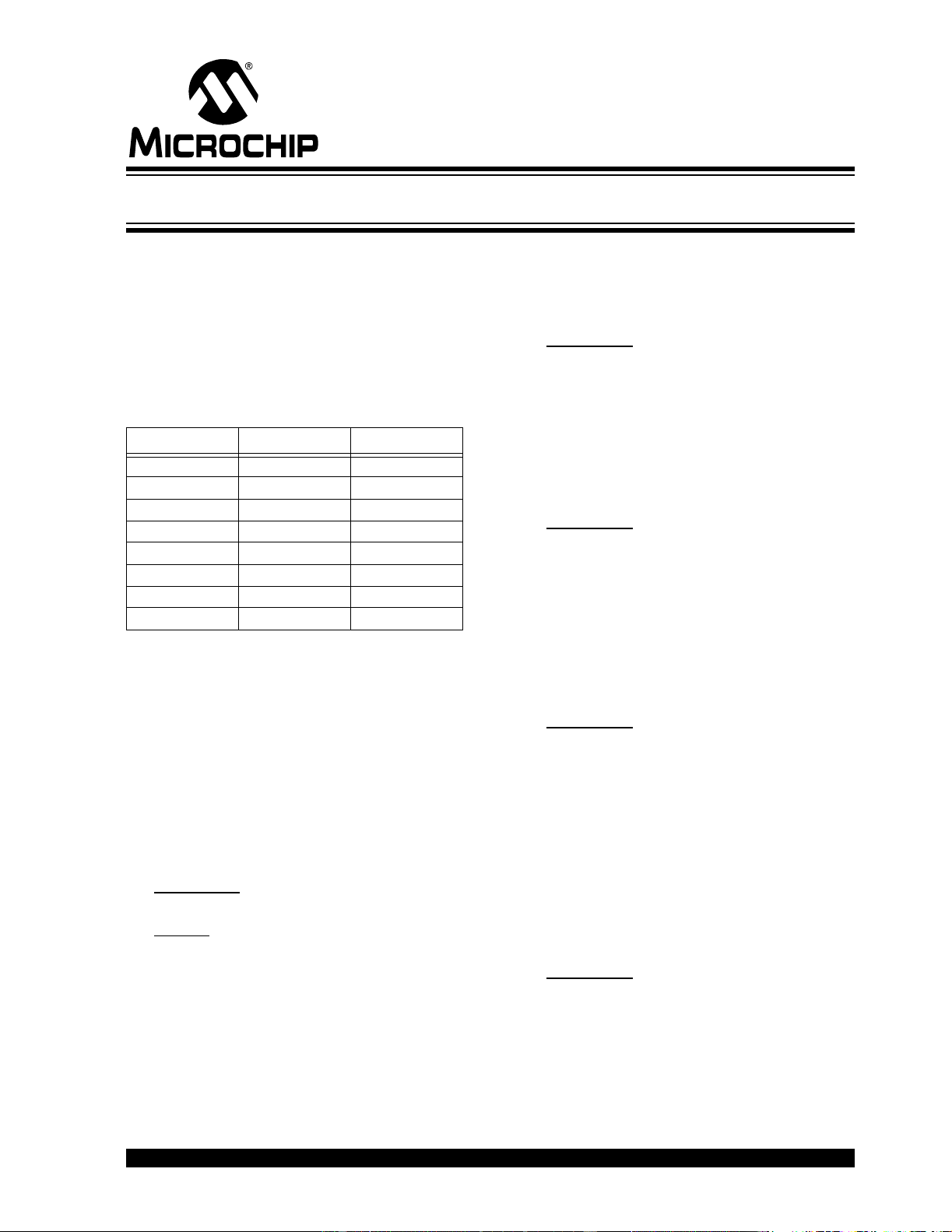

Part Number Device ID Revision ID

PIC18F24J10 0001 1101 000 0001

PIC18LF24J10 0001 1101 010 0001

PIC18F25J10 0001 1100 000 0001

PIC18LF25J10 0001 1100 010 0001

PIC18F44J10 0001 1101 001 0001

PIC18LF44J10 0001 1101 011 0001

PIC18F45J10 0001 1100 001 0001

PIC18LF45J10 0001 1100 011 0001

The Device IDs (DEVID1 and DEVID2) are located at

addresses 3FFFFEh:3FFFFFh in the device’s

configuration space. They are shown in hexadecimal

in the format “DEVID2 DEVID1”.

PIC18F24J10/25J10/44J10/45J10 Rev. A2 Silicon Errata

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件