Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F46K20-I/MV 数据手册 > PIC18F46K20-I/MV 其他数据使用手册 2/12 页

器件3D模型

器件3D模型¥ 6.867

PIC18F46K20-I/MV 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

UQFN-40

描述:

28 /40/ 44引脚闪存单片机采用纳瓦XLP技术 28/40/44-Pin Flash Microcontrollers with nanoWatt XLP Technology

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装信息在P9

导航目录

PIC18F46K20-I/MV数据手册

Page:

of 12 Go

若手册格式错乱,请下载阅览PDF原文件

PIC18F26K20/46K20

DS80000379C-page 2 2008-2015 Microchip Technology Inc.

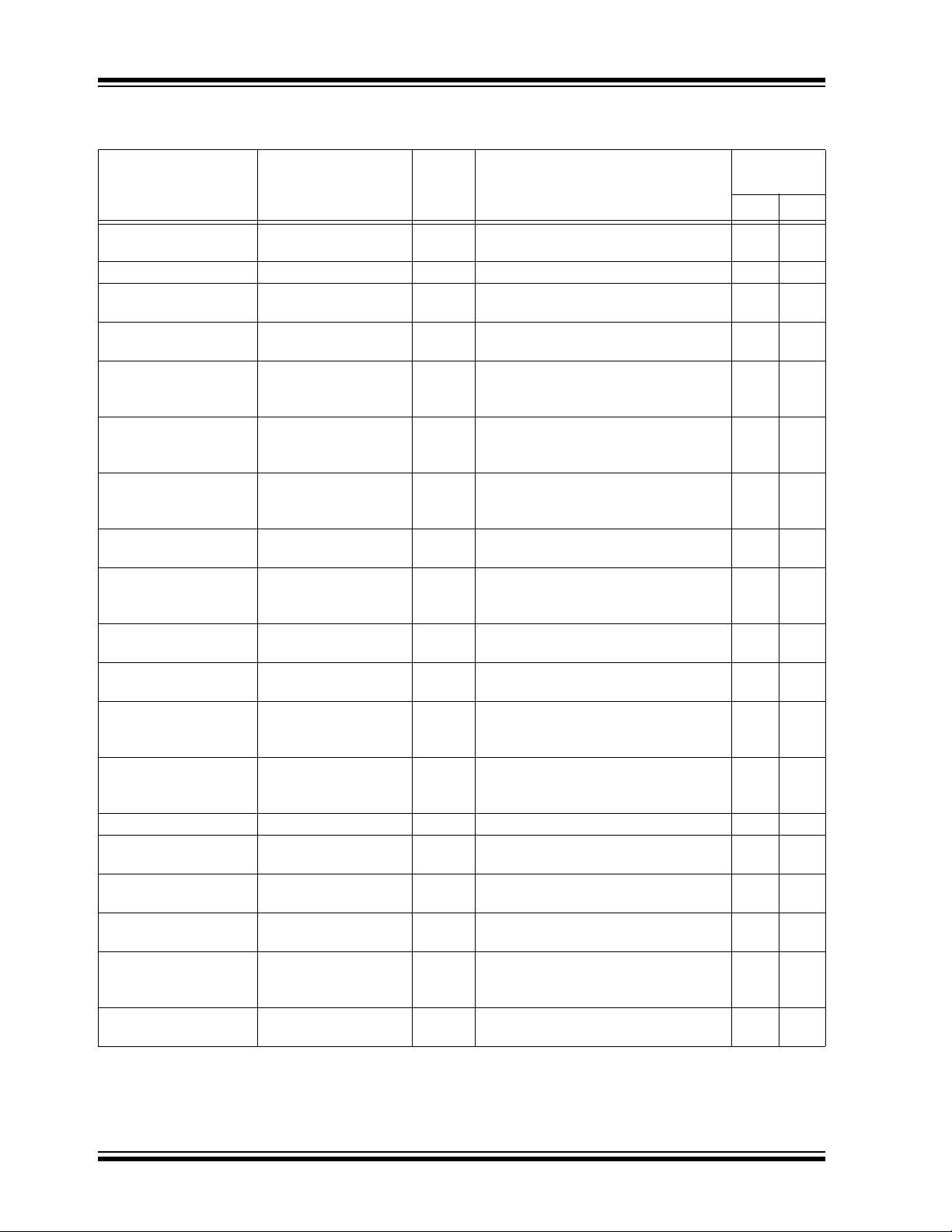

TABLE 2: SILICON ISSUE SUMMARY

Module Feature

Item

Number

Issue Summary

Affected

Revisions

(1)

A4 A5

ECCP ECCP Modes 1. Changing ECCP mode may cause a

false capture of TMR1 value.

XX

ECCP Full-Bridge 2. Compromised dead band. X X

MSSP I

2

C I

2

C 3. Slower slew rate than I

2

C

specifications.

XX

ADC ADC Conversion 4. Offset error is 3 LSb typical and 7 LSb

maximum.

XX

MSSP I

2

C I

2

C 5. False ACK generated when SSPOV bit

is set and a matching address is

clocked-in.

XX

MSSP I

2

C I

2

C Master 6. The first high-clock cycle following a

clock stretching event may be shorter

than half the clock period.

XX

MSSP I

2

C I

2

C Master Baud Rate 7. Unexpected operation may occur if

SSPADD is set to a value lower than

0x03.

XX

MSSP SPI SPI Clock 8. First SPI clock may be short if SPI clock

is configured to Timer2output/2.

XX

MSSP SPI SPI Master 9. When CKE is cleared and SMP is set,

the last bit of incoming data will not be

sampled properly.

XX

MSSP SPI SPI Master 10. SSPBUF will reload the SSPSR output

on every SS pin toggle, if CKE is set.

XX

MSSP SPI SPI Master 11. Erroneous output on SCK pin for

CKE = 1 and CKP = 0.

XX

EUSART Synchronous mode 12. Duty cycle of CK is skewed by one baud

count if SPBRG is set to an odd

number.

XX

EUSART Transmit Buffer 13. Data corruption may occur if TXREG is

written while TX shift register has some

characters in it for SPBRG = 3.

XX

EUSART Transmit mode 14.

Improper clock behavior for SPBRG =

0

.

XX

System Clocks HFINTOSC 15. HFINTOSC output frequency is 16 MHz

± 3%, 25°C to 85°C.

XX

POR/BOR Power-on Reset 16. Unexpected code execution may occur

below the BOR range.

XX

POR Power-on Reset 17. POR may release below the rearm

voltage for certain BOR voltages.

XX

POR Power-on Reset 18. Part may stay in Reset state if POR

triggers and then V

DD rises faster than

7500 volts per second.

XX

Clocks EC mode 19. EC Mode operation is limited to a

maximum of 48 MHz.

XX

Note 1: Only those issues indicated in the last column apply to the current silicon revision.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件