Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F66K80-I/MR 数据手册 > PIC18F66K80-I/MR 其他数据使用手册 1/598 页

器件3D模型

器件3D模型¥ 39.181

PIC18F66K80-I/MR 其他数据使用手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-64

描述:

MICROCHIP PIC18F66K80-I/MR 微控制器, 8位, 闪存, AEC-Q100, PIC18FxxKxx, 64 MHz, 64 KB, 4 KB, 64 引脚, QFN

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P4P5P6P7P44P251P253P262P264P266Hot

典型应用电路图在P242P244P285

原理图在P11P14P15P16P56P75P186P190P200P206P216P220

封装尺寸在P573

标记信息在P571P572

封装信息在P571P576P579P585P586P587

功能描述在P365

技术参数、封装参数在P165P546P547P548P549P551P552P553

应用领域在P262P268P275P380

电气规格在P11P45P78P134P165P368P373P374P376P378

导航目录

PIC18F66K80-I/MR数据手册

Page:

of 598 Go

若手册格式错乱,请下载阅览PDF原文件

2010-2017 Microchip Technology Inc. DS30009977G-page 1

Power-Managed Modes:

• Run: CPU on, Peripherals on

• Idle: CPU off, Peripherals on

• Sleep: CPU off, Peripherals off

• Two-Speed Oscillator Start-up

• Fail-Safe Clock Monitor (FSCM)

• Power-Saving Peripheral Module Disable (PMD)

• Ultra Low-Power Wake-up

• Fast Wake-up, 1 s, Typical

• Low-Power WDT, 300 nA, Typical

• Run mode Currents Down to Very Low 3.8 A, Typical

• Idle mode Currents Down to Very Low 880 nA, Typical

• Sleep mode Current Down to Very Low 13 nA, Typical

ECAN Bus Module Features:

• Conforms to CAN 2.0B Active Specification

• Three Operating modes:

- Legacy mode (full backward compatibility with

existing PIC18CXX8/FXX8 CAN modules)

- Enhanced mode

- FIFO mode or programmable TX/RX buffers

• Message Bit Rates up to 1 Mbps

• DeviceNet™ Data Byte Filter Support

• Six Programmable Receive/Transmit Buffers

• Three Dedicated Transmit Buffers with Prioritization

• Two Dedicated Receive Buffers

ECAN Bus Module Features (Continued):

• 16 Full, 29-Bit Acceptance Filters with Dynamic

Association

• Three Full, 29-Bit Acceptance Masks

• Automatic Remote Frame Handling

• Advanced Error Management Features

Special Microcontroller Features:

• Operating Voltage Range: 1.8V to 5.5V

• On-Chip 3.3V Regulator

• Operating Speed up to 64 MHz

• Up to 64 Kbytes On-Chip Flash Program Memory:

- 10,000 erase/write cycle, typical

- 20 years minimum retention, typical

• 1,024 Bytes of Data EEPROM:

- 100,000 Erase/write cycle data EEPROM

memory, typical

• 3.6 Kbytes of General Purpose Registers (SRAM)

• Three Internal Oscillators: LF-INTOSC (31 KHz),

MF-INTOSC (500 kHz) and HF-INTOSC (16 MHz)

• Self-Programmable under Software Control

• Priority Levels for Interrupts

• 8 x 8 Single-Cycle Hardware Multiplier

• Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 4,194s

• In-Circuit Serial Programming™ (ICSP™) via Two Pins

• In-Circuit Debug via Two Pins

• Programmable BOR

• Programmable LVD

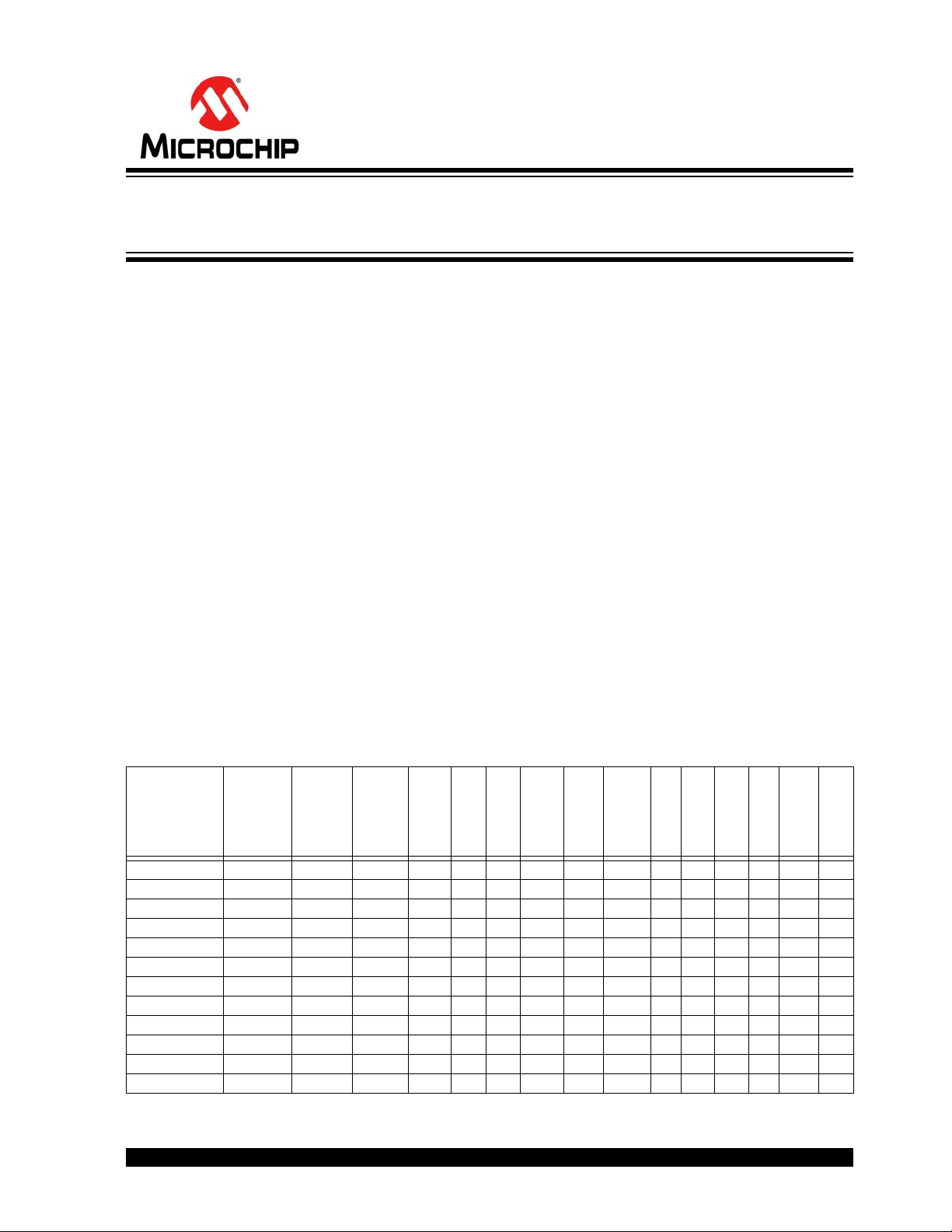

TABLE 1: DEVICE COMPARISON

Device

Program

Memory

Data

Memory

(Bytes)

Data EE

(Bytes)

Pins I/O

CTMU

12-Bit A/D

Channels

CCP/

ECCP

Timers

8-Bit/16-Bit

EUSART

Comparators

ECAN™

MSSP

BORMV/LVD

DSM

PIC18F25K80 32 Kbytes 3,648 1,024 28 24 1 8-ch 4/1 2/3 2 2 1 1 Yes No

PIC18LF25K80 32 Kbytes 3,648 1,024 28 24 1 8-ch 4/1 2/3 2 2 1 1 Yes No

PIC18F26K80 64 Kbytes 3,648 1,024 28 24 1 8-ch 4/1 2/3 2 2 1 1 Yes No

PIC18LF26K80 64 Kbytes 3,648 1,024 28 24 1 8-ch 4/1 2/3 2 2 1 1 Yes No

PIC18F45K80 32 Kbytes 3,648 1,024 40/44 35 1 11-ch 4/1 2/3 2 2 1 1 Yes No

PIC18LF45K80 32 Kbytes 3,648 1,024 40/44 35 1 11-ch 4/1 2/3 2 2 1 1 Yes No

PIC18F46K80 64 Kbytes 3,648 1,024 40/44 35 1 11-ch 4/1 2/3 2 2 1 1 Yes No

PIC18LF46K80 64 Kbytes 3,648 1,024 40/44 35 1 11-ch 4/1 2/3 2 2 1 1 Yes No

PIC18F65K80 32 Kbytes 3,648 1,024 64 54 1 11-ch 4/1 2/3 2 2 1 1 Yes Yes

PIC18LF65K80 32 Kbytes 3,648 1,024 64 54 1 11-ch 4/1 2/3 2 2 1 1 Yes Yes

PIC18F66K80 64 Kbytes 3,648 1,024 64 54 1 11-ch 4/1 2/3 2 2 1 1 Yes Yes

PIC18LF66K80 64 Kbytes 3,648 1,024 64 54 1 11-ch 4/1 2/3 2 2 1 1 Yes Yes

PIC18F66K80 FAMILY

28/40/44/64-Pin, Enhanced Flash Microcontrollers

with ECAN™ XLP Technology

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件