Datasheet 搜索 > 微控制器 > ST Microelectronics(意法半导体) > STM32F207ZGT6 数据手册 > STM32F207ZGT6 其他数据使用手册 5/8 页

器件3D模型

器件3D模型¥ 31.094

STM32F207ZGT6 其他数据使用手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

分类:

微控制器

封装:

LQFP-144

描述:

STMICROELECTRONICS STM32F207ZGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M3, 120 MHz, 1 MB, 132 KB, 144 引脚, LQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

应用领域在P2

导航目录

STM32F207ZGT6数据手册

Page:

of 8 Go

若手册格式错乱,请下载阅览PDF原文件

5

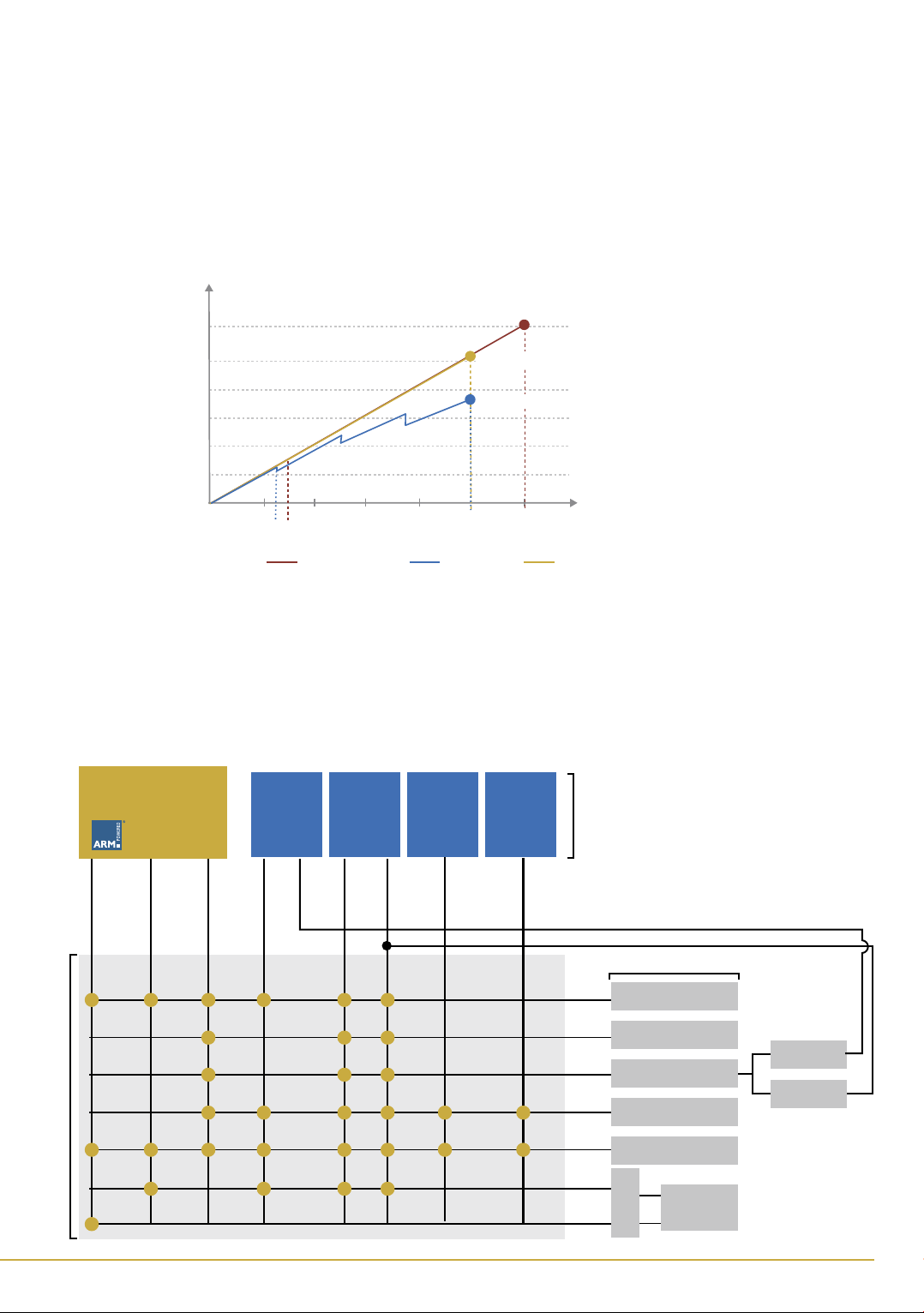

Combined with ST’s 90 nm technology, the ART Accelerator achieves a linear performance up to 120 MHz, offering 150 DMIPS

and 254 Coremark performance executing from Flash.

The acceleration mechanism is made possible using a prefetch queue, a branch cache and a smart arbitration mechanism.

MCUs using less advanced accelerators or slower embedded Flash memories will impact execution performance as wait

states occur.

MCUs using faster Flash but no branch cache acceleration to achieve performance usually show higher power consumption

as a result of more accesses to a power hungry Flash.

ART Accelerator™ performance result

STM32 F2 series Competitor F Competitor R

F

CPU

(MHz)

DMIPS

50

100

150

125

75

25

40

20

80

60 100

120

0

STM32 F2:

best mix, acceleration and speed

Competitor R: maximum frequency limitation

Competitor F: Flash access bottleneck

The 32-bit multi-AHB bus matrix allows concurrent execution and data transfers. It interconnects all masters and slaves and

ensures seamless and efficient operation even when several high-speed peripherals are working simultaneously.

For example, the following may all be performed at the same time.

The core accesses the Flash and 112-Kbyte SRAM block through the ART Accelerator

The DMA2 controller transfers data from the camera interface located on the AHB2 peripheral bus to an LCD connected to

the FSMC

The USB OTG High Speed interface stores received data in the 16-Kbyte SRAM block

General

purpose

DMA1

8 channels

General

purpose

DMA2

8 channels

Ethernet

MAC 10/100

DMA

USB OTG

HS

DMA

FSMC

Bus masters

100 Mbit/s

12.5 Mbyte/s

DMA_MEM2

DMA_P1

DMA_MEM1

DMA_P2

Instructions

Data

480 Mbyte/s

I

D

D

I

480 Mbyte/s

System

480 Mbit/s

60 Mbyte/s

Bus slaves

AHB2 peripheral

AHB1 peripheral

SRAM 16 Kbytes

Flash

1 Mbyte

Cortex-M3

with CPU

120 MHz

ART

Accelerator

SRAM 112 Kbytes

AHB1/APB1

AHB1/APB2

7-layer 32-bit multi-AHB bus matrix

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件