Datasheet 搜索 > 微处理器 > NXP(恩智浦) > T2080NXN8MQB 数据手册 > T2080NXN8MQB 其他数据使用手册 1/41 页

器件3D模型

器件3D模型¥ 2139.988

T2080NXN8MQB 其他数据使用手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

微处理器

封装:

FCBGA-896

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

T2080NXN8MQB数据手册

Page:

of 41 Go

若手册格式错乱,请下载阅览PDF原文件

1 About this document

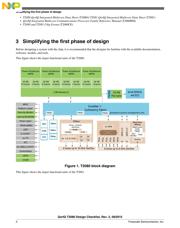

This document provides recommendations for new designs

based on the T2080, which is an advanced, multicore

processor that combines 4 dual-threaded e6500 processor

cores built on Power Architecture®, with high-performance

datapath acceleration logic and network and peripheral bus

interfaces required for networking, telecom/datacom, wireless

infrastructure, and mil/aerospace applications.

This document can also be used to debug newly-designed

systems by highlighting those aspects of a design that merit

special attention during initial system start-up.

NOTE

This document is also applicable to the

T2081. For a list of functionality

differences, see Appendix T2081 in the

T2080 Integrated Multicore

Communications Processor Family

Reference Manual (T2080RM).

2

Before you begin

Ensure you are familiar with the following Freescale collateral

before proceeding:

Freescale Semiconductor

Document Number: AN4804

Application Note

Rev. 2, 09/2015

QorIQ T2080 Design Checklist

Also supports the T2081

© 2013–2015 Freescale Semiconductor, Inc.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件