Datasheet 搜索 > 触发器 > Toshiba(东芝) > TC74HC74AF(F) 数据手册 > TC74HC74AF(F) 其他数据使用手册 1/11 页

器件3D模型

器件3D模型¥ 0.432

TC74HC74AF(F) 其他数据使用手册 - Toshiba(东芝)

制造商:

Toshiba(东芝)

分类:

触发器

封装:

SOP-14

描述:

TC74HC 系列,Toshiba工艺:CMOS 工作电压范围:2.0 至 6.0 V ### 74HC 系列

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1Hot

封装尺寸在P7P8P9P10

技术参数、封装参数在P3

电气规格在P4

导航目录

TC74HC74AF(F)数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

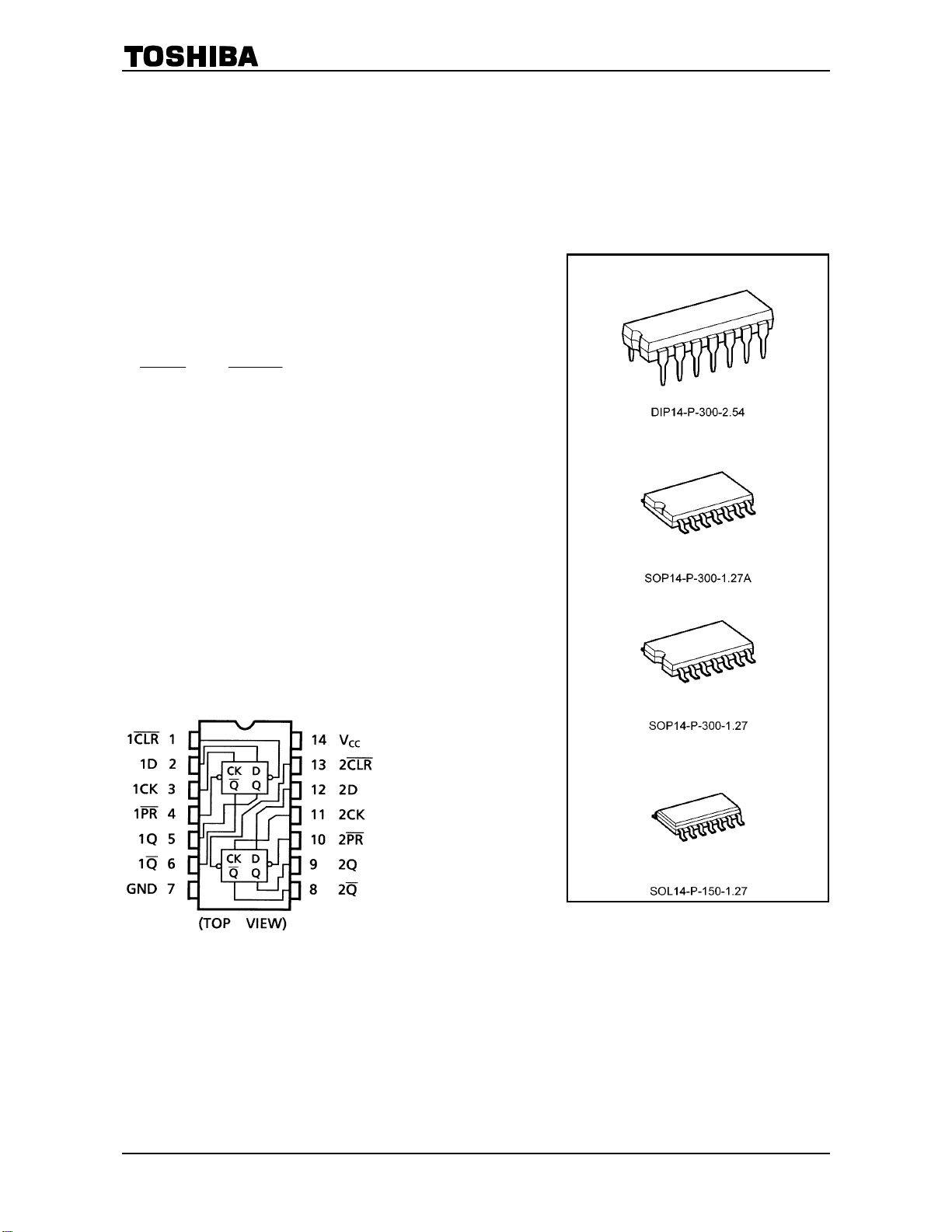

TC74HC74AP/AF/AFN

2006-02-01

1

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74HC74AP,TC74HC74AF,TC74HC74AFN

Dual D-Type Flip Flop Preset and Clear

The TC74HC74A is a high speed CMOS D FLIP FLOP

fabricated with silicon gate C

2

MOS technology.

It achieves the high speed operation similar to equivalent

LSTTL while maintaining the CMOS low power dissipation.

The signal level applied to the D INPUT is transferred to Q

OUTPUT during the positive going transition of the CLOCK

pulse.

CLEAR and PRESET are independent of the CLOCK and

are accomplished by setting the appropriate input to an “L” level.

All inputs are equipped with protection circuits against static

discharge or transient excess voltage.

Features

• High speed: f

max

= 77 MHz (typ.) at V

CC

= 5 V

• Low power dissipation: I

CC

= 2 µA (max) at Ta = 25°C

• High noise immunity: V

NIH

= V

NIL

= 28% V

CC

(min)

• Output drive capability: 10 LSTTL loads

• Symmetrical output impedance: |I

OH

| = I

OL

= 4 mA (min)

• Balanced propagation delays: t

pLH

∼

−

t

pHL

• Wide operating voltage range: V

CC

(opr) = 2~6 V

• Pin and function compatible with 74LS74

Pin Assignment

Note: xxxFN (JEDEC SOP) is not available in

Japan.

TC74HC74AP

TC74HC74AF

TC74HC74AFN

Weight

DIP14-P-300-2.54 : 0.96 g (typ.)

SOP14-P-300-1.27A : 0.18 g (typ.)

SOP14-P-300-1.27 : 0.18 g (typ.)

SOL14-P-150-1.27 : 0.12 g (typ.)

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件