Datasheet 搜索 > DSP数字信号处理器 > TI(德州仪器) > TMS320F2812PGFAG4 数据手册 > TMS320F2812PGFAG4 其他数据使用手册 6/31 页

器件3D模型

器件3D模型¥ 168.828

TMS320F2812PGFAG4 其他数据使用手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DSP数字信号处理器

封装:

LQFP-176

描述:

具有 150MHz 频率、256KB 闪存、EMIF 的 C2000™ 32 位 MCU 176-LQFP -40 to 85

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

标记信息在P5

技术参数、封装参数在P6P8P9P10P11P12P13P14P15P16P17P18

应用领域在P31

导航目录

TMS320F2812PGFAG4数据手册

Page:

of 31 Go

若手册格式错乱,请下载阅览PDF原文件

Usage Notes and Known Design Exceptions to Functional Specifications

www.ti.com

4 Usage Notes and Known Design Exceptions to Functional Specifications

4.1 Usage Notes

Usage notes highlight and describe particular situations where the device's behavior may not match

presumed or documented behavior. This may include behaviors that affect device performance or

functional correctness. These usage notes will be incorporated into future documentation updates for the

device (such as the device-specific data sheet), and the behaviors they describe will not be altered in

future silicon revisions.

Table 2 and Table 3 show which silicon revision(s) are affected by each usage note.

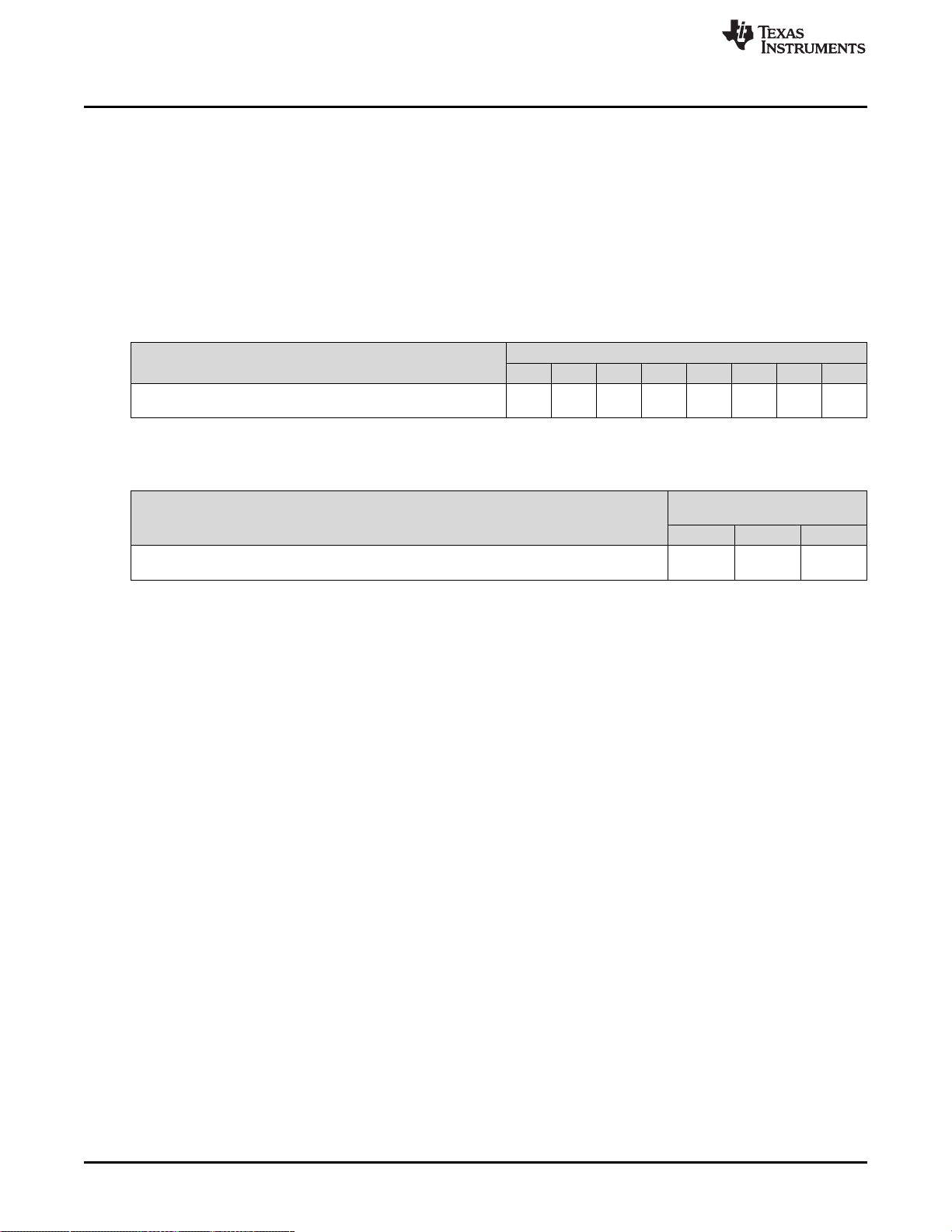

Table 2. List of Usage Notes for F281x

(1)

SILICON REVISION(S) AFFECTED

TITLE

0 A B C D E F G

PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write

Y Y Y Y Y Y Y Y

and Manual CPU Interrupt Mask Clear

(1)

Y = Yes

Table 3. List of Usage Notes for C281x

(1)

SILICON REVISION(S)

AFFECTED

TITLE

0 A B

PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt

Y Y Y

Mask Clear

(1)

Y = Yes

4.1.1 PIE: Spurious Nested Interrupt After Back-to-Back PIEACK Write and Manual CPU Interrupt

Mask Clear Usage Note

Revision(s) Affected: TMS320F281x: 0, A, B, C, D, E, F and G

TMS320C281x: 0, A, B

Certain code sequences used for nested interrupts allow the CPU and PIE to enter an inconsistent state

that can trigger an unwanted interrupt. The conditions required to enter this state are:

1. A PIEACK clear is followed immediately by a global interrupt enable (EINT or asm(" CLRC INTM")).

2. A nested interrupt clears one or more PIEIER bits for its group.

Whether the unwanted interrupt is triggered depends on the configuration and timing of the other

interrupts in the system. This is expected to be a rare or nonexistent event in most applications. If it

happens, the unwanted interrupt will be the first one in the nested interrupt's PIE group, and will be

triggered after the nested interrupt re-enables CPU interrupts (EINT or asm(" CLRC INTM")).

Workaround: Add a NOP between the PIEACK write and the CPU interrupt enable. Example code is

shown below.

//Bad interrupt nesting code

PieCtrlRegs.PIEACK.all = 0xFFFF; //Enable nesting in the PIE

EINT; //Enable nesting in the CPU

//Good interrupt nesting code

PieCtrlRegs.PIEACK.all = 0xFFFF; //Enable nesting in the PIE

asm(" NOP"); //Wait for PIEACK to exit the pipeline

EINT; //Enable nesting in the CPU

6

TMS320F281x, TMS320C281x Silicon Errata SPRZ193N–January 2003–Revised November 2015

Submit Documentation Feedback

Copyright © 2003–2015, Texas Instruments Incorporated

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件