Datasheet 搜索 > TVS二极管 > TI(德州仪器) > TPD2E009DBZR 数据手册 > TPD2E009DBZR 其他数据使用手册 1/18 页

¥ 0.432

TPD2E009DBZR 其他数据使用手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

TVS二极管

封装:

SOT-23-3

描述:

TEXAS INSTRUMENTS TPD2E009DBZR 静电保护装置, 8 V, SOT-23, 3 引脚, 5.5 V, 45 W

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

封装尺寸在P9P10P11

封装信息在P9P10P11

应用领域在P17

导航目录

TPD2E009DBZR数据手册

Page:

of 18 Go

若手册格式错乱,请下载阅览PDF原文件

1

FEATURES

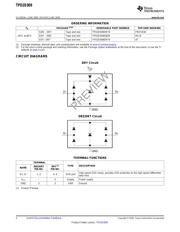

D+

3

1

2

D–

GND

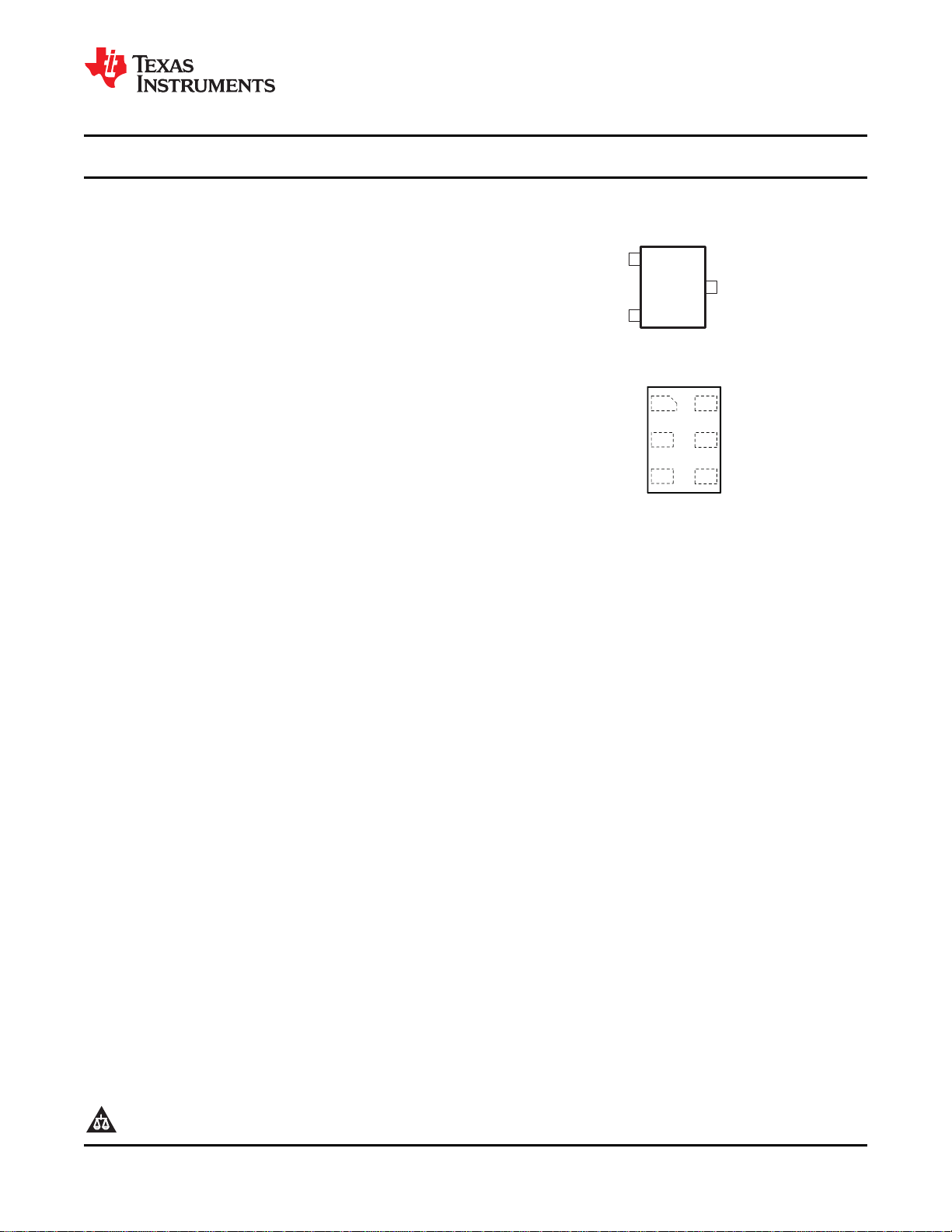

D+

V

CC

D–

1

2

3

4

5

6

N.C.

N.C.

GND

PREVIEW

APPLICATIONS

DESCRIPTION/ORDERING INFORMATION

TPD2E009

www.ti.com

.............................................................................................................................................................. SLVS953A – JUNE 2009 – REVISED JUNE 2009

2-CHANNEL ESD SOLUTION FOR HIGH-SPEED (6 GBPS) DIFFERENTIAL INTERFACE

DBZ/DRT PACKAGE

• 0.05-pF Matching Capacitance Between the

(TOP VIEW)

Differential Signal Pair

• Single-Pair Differential Lines to Protect the

Differential Data and Clock Lines of the LVDS,

SATA, Ethernet, or USB High-Speed (HS)

Interface

• Flow-Through Pin Mapping for the High-Speed

DRY PACKAGE

Lines Ensures Zero Additional Skew Due to

(TOP VIEW)

Board Layout While Placing ESD-Protection

Chip Near the Connector

• Supports Data Rates in Excess of 6 Gbps

• ESD Protection Meets or Exceeds

IEC61000-4-2 (Level 4)

• 5-A Peak Pulse Current (8/20 µ s Pulse) for

V

BUS

and D+, D – , and ID Lines

N.C. – No internal connection

• Industrial Temperature Range: – 40 ° C to 85 ° C

• Multiple Space-Saving Package Options

• Notebooks

• Set-Top Boxes

• DVD Players

• Media Players

• Portable Computers

The TPD2E009 provides 2 ESD clamp circuits with flow-through pin mapping for ease of board layout. This

device has been designed to protect sensitive components which are connected to ultra high-speed data and

transmission lines. The TPD2E009 offers protection from stress caused by ESD (electrostatic discharge). This

device also offers 5 A (8/20 µ s) peak pulse current ratings per IEC 61000-4-5 (lightning) specification.

The monolithic silicon technology allows matching between the differential signal pairs. The less than differential

0.05-pF capacitance ensures that the differential signal distortion due to added ESD clamp remains minimal. The

0.7-pF line capacitance is suitable for high-speed data rate (in excess of 6 Gbps).

The TPD2E009 conforms to IEC61000-4-2 (Level 4) ESD protection. The DRT (1 mm × 1 mm) package is

offered for space-saving portable applications. The industry standard DBZ (2.4 mm × 2.9 mm) package offers

additional flexibility in the board layout for the system designer.

The TPD2E009 is characterized for operation over ambient air temperature range of – 40 ° C to 85 ° C.

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 2009, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件