Datasheet 搜索 > 时钟发生器 > ADI(亚德诺) > ADF4118BRUZ 数据手册 > ADF4118BRUZ 产品设计参考手册 1/28 页

器件3D模型

器件3D模型¥ 0.072

ADF4118BRUZ 产品设计参考手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

时钟发生器

封装:

TSSOP-16

描述:

ANALOG DEVICES ADF4118BRUZ 芯片, 频率合成器, 3GHZ, TSSOP-16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P19P20P21

导航目录

ADF4118BRUZ数据手册

Page:

of 28 Go

若手册格式错乱,请下载阅览PDF原文件

EV-ADF411XSD1Z User Guide

UG-161

One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

Evaluation Board for the Integer-N and Fractional-N PLL Frequency Synthesizer

PLEASE SEE THE LAST PAGE FOR AN IMPORTANT

WARNING AND LEGAL TERMS AND CONDITIONS.

Rev. A | Page 1 of 28

FEATURES

General-purpose PLL evaluation board, excluding the

frequency synthesizer, VCO, and loop filter

Compatible with integer-N PLLs in a 16-lead TSSOP package

ADF4110, ADF4111, ADF4112, ADF4113, ADF4116,

ADF4117, ADF4118, ADF4106, ADF4107

Compatible with fractional-N PLLs in a 16-lead TSSOP package

ADF4153, ADF4154, ADF4156, ADF4157

Accompanying software allows complete control of synthesizer

functions from a PC

EVALUATION KIT CONTENTS

EV-ADF411XSD1Z board

CD that includes

Self-installing software that allows users to control the

board and exercise all functions of the device

Electronic version of the frequency synthesizer data sheet

Electronic version of the UG-161 user guide

ADDITIONAL EQUIPMENT

PC running Windows XP or more recent version

SDP-S board (system demonstration platform-serial)

ADF41XXBRUZ (see the Features section for applicable parts)

T-package VCO, loop filter components

Spectrum analyzer, oscilloscope (optional)

DOCUMENTS NEEDED

Frequency synthesizer data sheet

UG-161 user guide

REQUIRED SOFTWARE

Analog Devices Int-N PLL software (Version 7 or higher)

Analog Devices Frac-N PLL software (Version 4 or higher)

ADIsimPLL

GENERAL DESCRIPTION

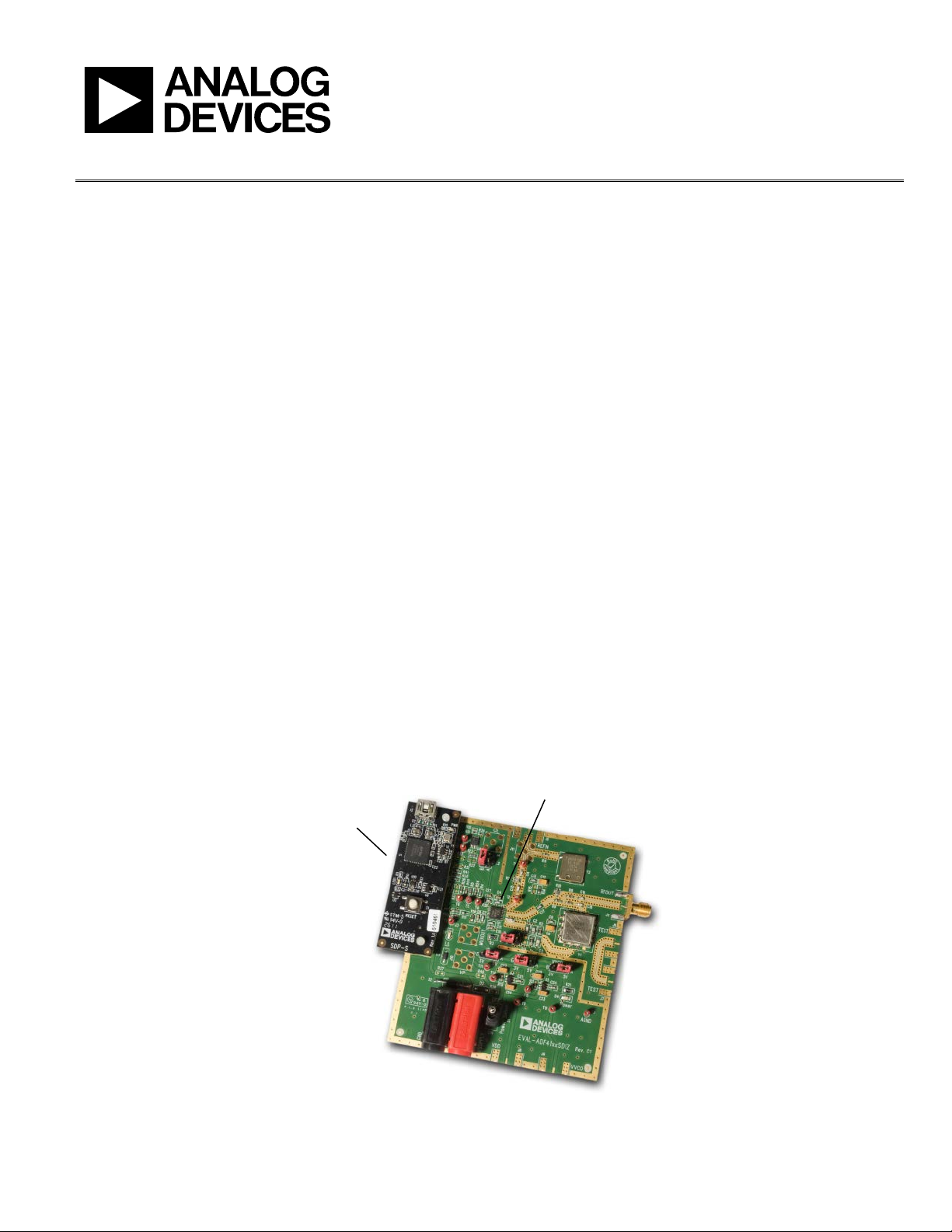

This evaluation board allows the user to evaluate the performance

of the ADF41XXBRUZ frequency synthesizers, which are available

in 16-lead TSSOP packages. The

SDP-S controller board allows

software programming of the frequency synthesizer. Figure 1

shows the board, which contains footprints for a frequency

synthesizer, the power supplies, a TCXO reference, and an RF

output. There are also footprints for the passive PLL loop filter

components, a VCO, and an external reference SMA input.

The PLL loop filter values can be generated from the Analog

Devices, Inc.,

ADIsimPLL software tool. Prior to evaluation

setup, the ADF41XXBRUZ, T-package VCO, and loop filter

components should be inserted on the board.

Figure 1 shows the board with all necessary components inserted.

EVALUATION BOARD

Figure 1. EV-ADF411XSD1Z with SDP-S

09146-001

SDP-S

(TO BE PURCHASED

SEPARATELY)

ADF41XXBRUZ

(SAMPLES TO BE PURCHASED SEPARATELY)

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件