Datasheet 搜索 > ST Microelectronics(意法半导体) > IIS2MDCTR 数据手册 > IIS2MDCTR 产品设计参考手册 5/9 页

器件3D模型

器件3D模型¥ 11.915

IIS2MDCTR 产品设计参考手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

封装:

LGA-12

描述:

板机接口霍耳效应/磁性传感器 High accuracy, ultra-low-power ,3-axis digital output magnetometer

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

IIS2MDCTR数据手册

Page:

of 9 Go

若手册格式错乱,请下载阅览PDF原文件

DocID12707 Rev 6 5/9

TN0018 PCB design guidelines

9

2.1 PCB design rules

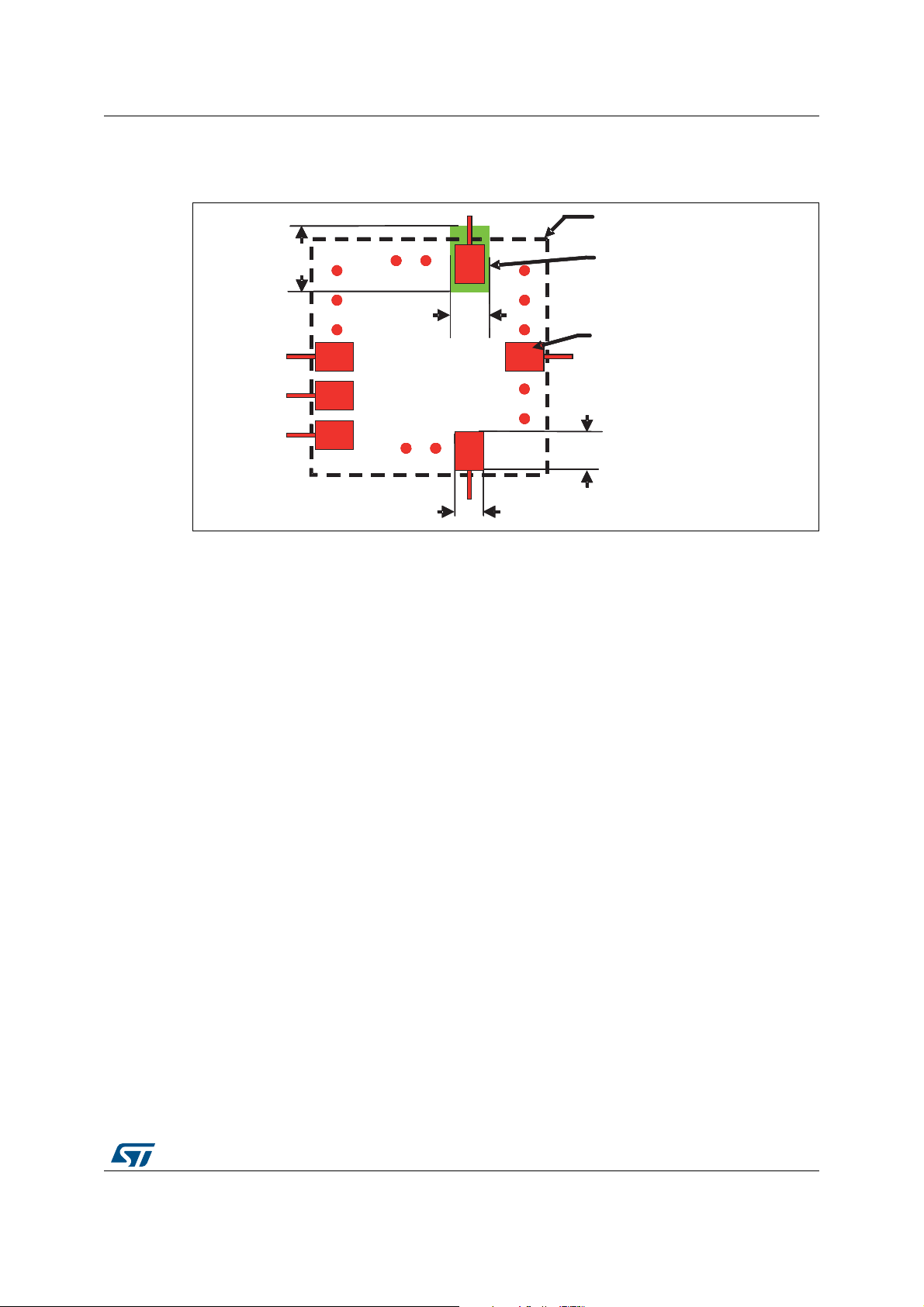

Figure 1. Recommended land and solder mask design for LGA packages

PCB land design and connecting traces should be designed symmetrically.

For LGA pin spacing greater than 200 μm:

A = PCB land length = LGA solder pin length + 0.1 mm

B = PCB land width = LGA solder pin width + 0.1 mm

For LGA pin spacing equal to or less than 200 μm:

A = PCB land length = LGA solder pin length

B = PCB land width = LGA solder pin width

C = Solder mask opening length (when applicable) = PCB land length + 0.1 mm

D = Solder mask opening width = PCB land width + 0.1 mm

Package

footprint

A

B

Solder mask opening

external to land footprint:

recommended to

increase device to PCB

clearance

PCB land

C

D

Package

footprint

Solder mask opening

external to land footprint:

increase device to PCB

clearance

PCB land

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件