Datasheet 搜索 > Micron(镁光) > JS28F128P33B85 数据手册 > JS28F128P33B85 产品设计参考手册 1/253 页

器件3D模型

器件3D模型¥ 0

JS28F128P33B85 产品设计参考手册 - Micron(镁光)

制造商:

Micron(镁光)

封装:

TSSOP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P11P223P224P225P226P227P228P229P230P231P232P233Hot

典型应用电路图在P143

原理图在P3

封装尺寸在P251P252

标记信息在P251P252

封装信息在P2P10P249P251P252

功能描述在P120P241P242

技术参数、封装参数在P43P44P45P46P47P48P49P50P51P52P53P54

应用领域在P1P2P131P244P253

电气规格在P45P54P74P77P120

导航目录

JS28F128P33B85数据手册

Page:

of 253 Go

若手册格式错乱,请下载阅览PDF原文件

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

F28M36P63C2

,

F28M36P53C2

,

F28M36H53C2

,

F28M36H53B2

F28M36H33C2, F28M36H33B2

SPRS825D –OCTOBER 2012–REVISED OCTOBER 2015

F28M36x Concerto™ Microcontrollers

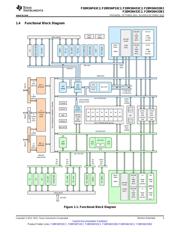

1 Device Overview

1.1 Features

1

• Master Subsystem — ARM

®

Cortex

®

-M3 • Control Subsystem — TMS320C28x 32-Bit CPU

– 125 MHz – 150 MHz

– Embedded Memory – C28x Core Hardware Built-in Self-Test

– Embedded Memory

• Up to 1MB of Flash (ECC)

• Up to 512KB of Flash (ECC)

• Up to 128KB of RAM (ECC or Parity)

• Up to 36KB of RAM (ECC or Parity)

• Up to 64KB of Shared RAM

• Up to 64KB of Shared RAM

• 2KB of IPC Message RAM

– Five Universal Asynchronous • 2KB of IPC Message RAM

Receiver/Transmitters (UARTs)

– IEEE-754 Single-Precision Floating-Point Unit

– Four Synchronous Serial Interfaces (SSIs) (FPU)

and a Serial Peripheral Interface (SPI)

– Viterbi, Complex Math, CRC Unit (VCU)

– Two Inter-integrated Circuits (I

2

Cs)

– Serial Communications Interface (SCI)

– Universal Serial Bus On-the-Go (USB-OTG) +

– SPI

PHY

– I

2

C

– 10/100 ENET 1588 MII

– 6-Channel Direct Memory Access (DMA)

– Two Controller Area Network, D_CAN, Modules

– 12 Enhanced Pulse Width Modulator (ePWM)

(Pin-Bootable)

Modules

– 32-Channel Micro Direct Memory Access

• 24 Outputs (16 High-Resolution)

(µDMA)

– Six 32-Bit Enhanced Capture (eCAP) Modules

– Dual Security Zones (128-Bit Password per

– Three 32-Bit Enhanced Quadrature Encoder

Zone)

Pulse (eQEP) Modules

– External Peripheral Interface (EPI)

– Multichannel Buffered Serial Port (McBSP)

– Micro Cyclic Redundancy Check (µCRC)

– EPI

Module

– One Security Zone (128-Bit Password)

– Four General-Purpose Timers

– Three 32-Bit Timers

– Two Watchdog Timer Modules

– Endianness: Little Endian

– Endianness: Little Endian

• Analog Subsystem

• Clocking

– Dual 12-Bit Analog-to-Digital Converters (ADCs)

– On-chip Crystal Oscillator and External Clock

– Up to 2.88 MSPS

Input

– Up to 24 Channels

– Dynamic Phase-Locked Loop (PLL) Ratio

– Four Sample-and-Hold (S/H) Circuits

Changes Supported

– Up to Six Comparators With 10-Bit Digital-to-

• 1.2-V Digital, 1.8-V Analog, 3.3-V I/O Design

Analog Converter (DAC)

• Interprocessor Communications (IPC)

• Package

– 32 Handshaking Channels

– 289-Ball ZWT New Fine Pitch Ball Grid Array

– Four Channels Generate IPC Interrupts

(nFBGA)

– Can be Used to Coordinate Transfer of Data

• Temperature Options:

Through IPC Message RAMs

– T: –40ºC to 105ºC Junction

• Up to 142 Individually Programmable, Multiplexed

– S: –40ºC to 125ºC Junction

General-Purpose Input/Output (GPIO) Pins

– Q: –40ºC to 125ºC Free-Air

– Glitch-free I/Os

(Q100 Qualification for Automotive Applications)

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件