Datasheet 搜索 > 16位微控制器 > Freescale(飞思卡尔) > MC9S12DG256CPVE 数据手册 > MC9S12DG256CPVE 产品设计参考手册 5/132 页

器件3D模型

器件3D模型¥ 167.071

MC9S12DG256CPVE 产品设计参考手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

分类:

16位微控制器

封装:

LQFP-112

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MC9S12DG256CPVE数据手册

Page:

of 132 Go

若手册格式错乱,请下载阅览PDF原文件

MC9S12DT256 Device User Guide — V03.07

5

Table of Contents

Section 1 IntroductionMC9S12DT256

1.1 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

1.5 Device Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

1.6 Detailed Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

1.7 Part ID Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

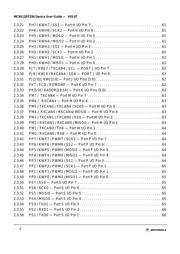

Section 2 Signal Description

2.1 Device Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

2.2 Signal Properties Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

2.3 Detailed Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

2.3.1 EXTAL, XTAL — Oscillator Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

2.3.2 RESET — External Reset Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

2.3.3 TEST — Test Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

2.3.4 VREGEN — Voltage Regulator Enable Pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

2.3.5 XFC — PLL Loop Filter Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

2.3.6 BKGD / TAGHI / MODC — Background Debug, Tag High, and Mode Pin . . . . . . . .57

2.3.7 PAD15 / AN15 / ETRIG1 — Port AD Input Pin of ATD1 . . . . . . . . . . . . . . . . . . . . . .57

2.3.8 PAD[14:08] / AN[14:08] — Port AD Input Pins of ATD1 . . . . . . . . . . . . . . . . . . . . . .57

2.3.9 PAD7 / AN07 / ETRIG0 — Port AD Input Pin of ATD0 . . . . . . . . . . . . . . . . . . . . . . .58

2.3.10 PAD[06:00] / AN[06:00] — Port AD Input Pins of ATD0 . . . . . . . . . . . . . . . . . . . . . .58

2.3.11 PA[7:0] / ADDR[15:8] / DATA[15:8] — Port A I/O Pins . . . . . . . . . . . . . . . . . . . . . . .58

2.3.12 PB[7:0] / ADDR[7:0] / DATA[7:0] — Port B I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . .58

2.3.13 PE7 / NOACC / XCLKS — Port E I/O Pin 7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

2.3.14 PE6 / MODB / IPIPE1 — Port E I/O Pin 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

2.3.15 PE5 / MODA / IPIPE0 — Port E I/O Pin 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

2.3.16 PE4 / ECLK — Port E I/O Pin 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

2.3.17 PE3 / LSTRB / TAGLO — Port E I/O Pin 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

2.3.18 PE2 / R/W — Port E I/O Pin 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

2.3.19 PE1 / IRQ — Port E Input Pin 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

2.3.20 PE0 / XIRQ — Port E Input Pin 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件