Datasheet 搜索 > 微控制器 > TI(德州仪器) > TMS320F28066PZPS 数据手册 > TMS320F28066PZPS 产品设计参考手册 3/177 页

器件3D模型

器件3D模型¥ 495.264

TMS320F28066PZPS 产品设计参考手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

微控制器

封装:

HTQFP-100

描述:

Piccolo微处理器 Piccolo Microcontrollers

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P9P82Hot

典型应用电路图在P46P97

原理图在P3P80P94P99P108P120P134P136P139

封装尺寸在P172P173P174P175

标记信息在P172P173P174P175P176

封装信息在P2P163P172P173P174P175P176

技术参数、封装参数在P19P20P21P22P23P24P25P26P27P28P29P30

应用领域在P2P72P133P137P156P157P158P177

电气规格在P20P86P95

型号编号列表在P120

导航目录

TMS320F28066PZPS数据手册

Page:

of 177 Go

若手册格式错乱,请下载阅览PDF原文件

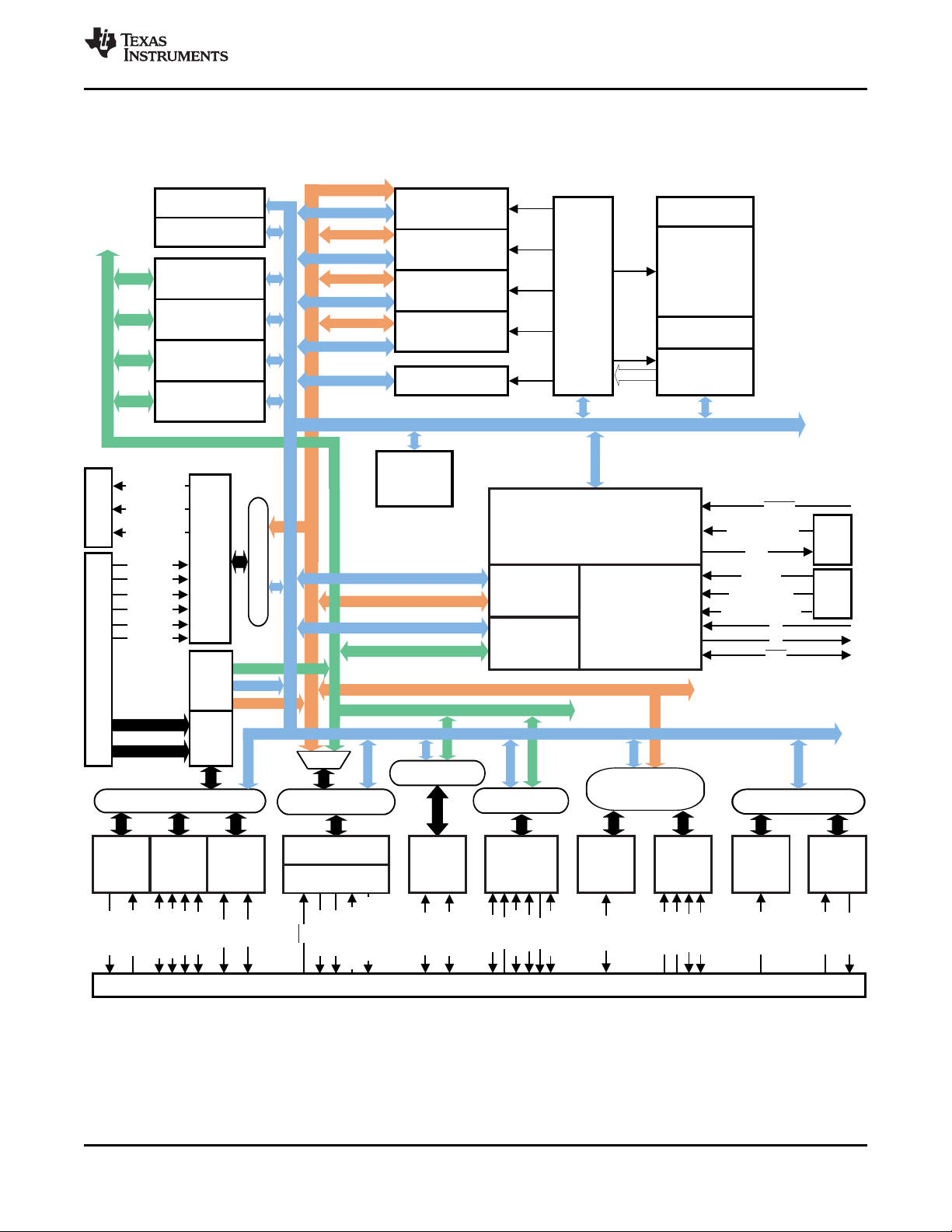

CLA Bus

DMA Bus

DMA Bus

16-bit Peripheral Bus

32-bit Peripheral

Bus

Memory Bus

A7:0

B7:0

Memory Bus

Memory Bus

DMA Bus

CLA Bus

DMA Bus

GPIO Mux

AIO Mux

32-bit Peripheral Bus

ADC

0-wait

Result

Regs

ADC

COMP

+

DAC

COMP1OUT

COMP2OUT

COMP3OUT

COMP1A

COMP2A

COMP3A

COMP1B

COMP2B

COMP3B

Boot-ROM

(32K 16)

(0-wait,

Non-Secure)

´

GPIO

Mux

GPIO

Mux

TRST

TCK, TDI, TMS

TDO

XCLKIN

LPM Wakeup

3 Ext. Interrupts

X1

X2

XRS

M0 SARAM (1K 16)

(0-wait, Non-Secure)

´

M1 SARAM (1K 16)

(0-wait, Non-Secure)

´

L5 DPSARAM (8K 16)

(0-wait, Non-Secure)

DMA RAM0

´

L6 DPSARAM (8K 16)

(0-wait, Non-Secure)

DMA RAM1

´

L7 DPSARAM (8K 16)

(0-wait, Non-Secure)

DMA RAM2

´

L8 DPSARAM (8K 16)

(0-wait, Non-Secure)

DMA RAM3

´

L0 DPSARAM (2K 16)

(0-wait, Secure)

CLA Data RAM2

´

L1 DPSARAM (1K 16)

(0-wait, Secure)

CLA Data RAM0

´

L2 DPSARAM (1K 16)

(0-wait, Secure)

CLA Data RAM1

´

L3 DPSARAM (4K 16)

(0-wait, Secure)

CLA Program RAM

´

L4 SARAM (8K 16)

(0-wait, Secure)

´

Code

Security

Module

(CSM)

PSWD

OTP 1K 16

Secure

´

FLASH

128K 16

8 equal sectors

Secure

´

64K 16´

PUMP

OTP/Flash

Wrapper

32-bit Peripheral

Bus

USB-0

GPIO Mux

SCITXDx

SCIRXDx

SPISIMOx

SPISOMIx

SPICLKx

SPISTEx

SDAx

SCLx

MFSRA

MDRA

MCLKRA

MFSXA

MDXA

MCLKXA

ECAPx

EQEPxA

EQEPxB

EQEPxI

EQEPxS

HRCAPx

CANRXx

CANTXx

USB0DP

USB0DM

TZx

EPWMxA

EPWMxB

EPWMSYNCI

EPWMSYNCO

SCI-A

SCI-B

(4L FIFO)

SPI-A

SPI-B

(4L FIFO)

I2C-A

(4L FIFO)

32-bit Peripheral Bus

(CLA accessible)

ePWM1 to ePWM8

HRPWM (8ch)

McBSP-A

32-bit

Peripheral Bus

(CLA accessible)

eCAP1

eCAP2

eCAP3

eQEP1

eQEP2

32-bit Peripheral

Bus

HRCAP1

HRCAP2

HRCAP3

HRCAP4

eCAN-A

(32-mbox)

CLA +

Message

RAMs

DMA

6-ch

C28x 32-bit CPU

FPU

VCU

OSC1, OSC2,

Ext, PLLs,

LPM, WD,

CPU Timer 0,

CPU Timer 1,

CPU Timer 2,

PIE

3

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Device OverviewCopyright © 2010–2016, Texas Instruments Incorporated

1.4 Functional Block Diagram

Figure 1-1 shows a functional block diagram of the device.

A. Not all peripheral pins are available at the same time due to multiplexing.

Figure 1-1. Functional Block Diagram

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件