Datasheet 搜索 > Microchip(微芯) > ATF16V8B-10PC 数据手册 > ATF16V8B-10PC 用户编程技术手册 6/16 页

器件3D模型

器件3D模型¥ 14.604

ATF16V8B-10PC 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

封装:

DIP-20

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ATF16V8B-10PC数据手册

Page:

of 16 Go

若手册格式错乱,请下载阅览PDF原文件

Functional Logic Diagram Description

The Logic Option and Functional Diagrams describe the

ATF16V8B architecture. Eight configurable macrocells

can be configured as a registered output, combinatorial

I/O, combinatorial output, or dedicated input.

The ATF16V8B can be configured in one of three different

modes. Each mode makes the ATF16V8B look like a dif-

ferent device. Most PLD compilers can choose the right

mode automatically. The user can also force the selection

by supplying the compiler with a mode selection. The de-

termining factors would be the usage of register versus

combinatorial outputs and dedicated outputs versus out-

puts with output enable control.

The ATF16V8B universal architecture can be pro-

grammed to emulate many 20-pin PAL devices. These

architectural subsets can be found in each of the configu-

ration modes described in the following pages. The user

can download the listed subset device JEDEC program-

ming file to the PLD programmer, and the ATF16V8B can

be configured to act like the chosen device. Check with

your programmer manufacturer for this capability.

Unused product terms are automatically disabled by the

compiler to decrease power consumption. A Security

Fuse, when programmed, protects the content of the

ATF16V8B. Eight bytes (64 fuses) of User Signature are

accessible to the user for purposes such as storing project

name, part number, revision, or date. The User Signature

is accessible regardless of the state of the Security Fuse.

Compiler Mode Selection

Registered Complex Simple Auto Select

ABEL, Atmel-ABEL

P16V8R P16V8C P16V8AS P16V8

CUPL

G16V8MS G16V8MA G16V8AS G16V8A

LOG/iC

GAL16V8_R

(1)

GAL16V8_C7

(1)

GAL16V8_C8

(1)

GAL16V8

OrCAD-PLD

“Registered” “Complex” “Simple” GAL16V8A

PLDesigner

P16V8R P16V8C P16V8C P16V8A

Tango-PLD

G16V8R G16V8C G16V8AS G16V8

Note: 1. Only applicable for version 3.4 or lower.

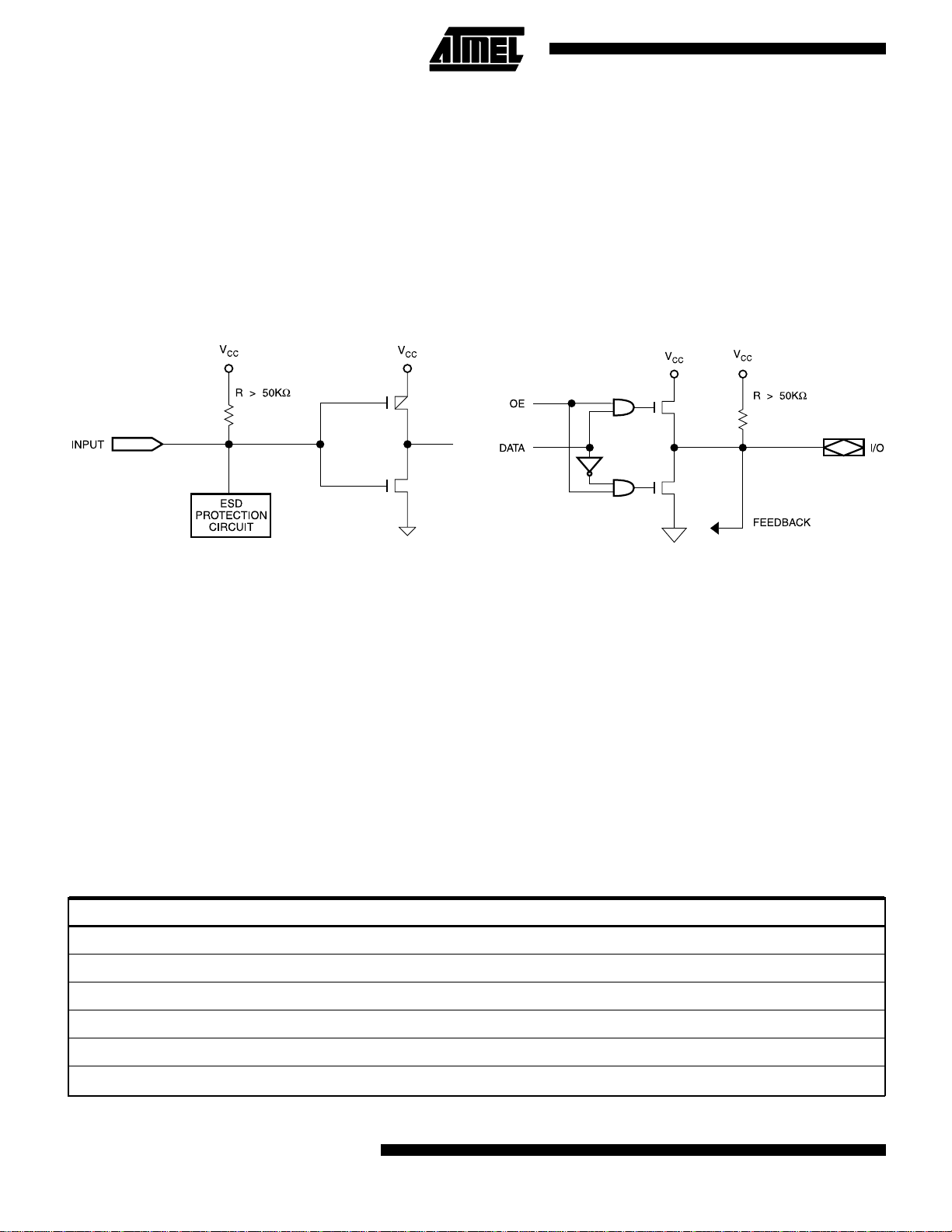

Input and I/O Pull-Ups

All ATF16V8B family members have internal input and I/O

pull-up resistors. Therefore, whenever inputs or I/Os are

not being driven externally, they will float to V

CC

. This en-

sures that all logic array inputs are at known states.

These are relatively weak active pull-ups that can easily

be overdriven by TTL-compatible drivers (see input and

I/O diagrams below).

Input Diagram

I/O Diagram

Programming/Erasing

Programming/erasing is performed using standard PLD

programmers. See

CMOS PLD Programming Hardware &

Software Support

for information on software/program-

ming.

Electronic Signature Word

There are 64 bits of programmable memory that are al-

ways available to the user, even if the device is secured.

These bits can be used for user-specific data.

1-12

ATF16V8B

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件