Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > ATMEGA1281V-8MUR 数据手册 > ATMEGA1281V-8MUR 用户编程技术手册 4/34 页

器件3D模型

器件3D模型¥ 50.823

ATMEGA1281V-8MUR 用户编程技术手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

VQFN-64

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ATMEGA1281V-8MUR数据手册

Page:

of 34 Go

若手册格式错乱,请下载阅览PDF原文件

4

ATmega640/V-1280/V-1281/V-2560/V-2561/V [SUMMARY]

2549QS–AVR–02/2014

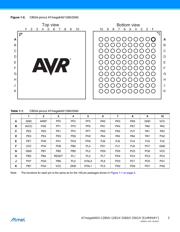

Figure 1-3. Pinout ATmega1281/2561

Note: The large center pad underneath the QFN/MLF package is made of metal and internally connected to GND. It should

be soldered or glued to the board to ensure good mechanical stability. If the center pad is left unconnected, the pack-

age might loosen from the board.

(RXD0/PCINT8/PDI) PE0

(TXD0/PDO) PE1

(XCK0/AIN0) PE2

(OC3A/AIN1) PE3

(OC3B/INT4) PE4

(OC3C/INT5) PE5

(T3/INT6) PE6

(ICP3/CLKO/INT7) PE7

(SS/PCINT0) PB0

(OC0B) PG5

(SCK/ PCINT1) PB1

(MOSI/ PCINT2) PB2

(MISO/ PCINT3) PB3

(OC2A/ PCINT4) PB4

(OC1A/PCINT5) PB5

(OC1B/PCINT6) PB6

(OC0A/OC1C/

PCINT7

) PB7

(TOSC2) PG3

(TOSC1) PG4

RESET

VCC

GND

XTAL2

XTAL1

(SCL/INT0) PD0

(SDA/INT1) PD1

(RXD1/INT2) PD2

(TXD1/INT3) PD3

(ICP1) PD4

(XCK1) PD5

PA3 (AD3)

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PG2 (ALE)

PC7 (A15)

PC6 (A14)

PC5 (A13)

PC4 (A12)

PC3 (A11)

PC2 (A10)

PC1 (A9)

PC0 (A8)

PG1 (RD)

PG0 (WR)

AVCC

GND

AREF

PF0 (ADC0)

PF1 (ADC1)

PF2 (ADC2)

PF3 (ADC3)

PF4 (ADC4/TCK)

PF5 (ADC5/TMS)

PF6 (ADC6/TDO)

PF7 (ADC7/TDI)

GND

VCC

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

(T1) PD6

(T0) PD7

INDEX CORNER

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件