Datasheet 搜索 > 微控制器 > Microchip(微芯) > ATMEGA32-16AU 数据手册 > ATMEGA32-16AU 用户编程技术手册 1/27 页

器件3D模型

器件3D模型¥ 13.477

ATMEGA32-16AU 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-44

描述:

8 位 megaAVR 微控制器,32KB 到 256KB 闪存我们在 RS Components 提供多款来自 Atmel 的 megaAVR 8 位微控制器。 每个微控制器均基于增强型 RISC 体系结构,并具有 QTouch 库支持。 所有微控制器类型具有不同 Kb 的系统内可编程内存、EEPROM 和 SRAM 以及不同引脚和封装类型。 **megaAVR 8 位微控制器类型** ATmega32 ATmega64 ATmega128 ATmega324 ATmega325 ATmega406 ATmega640 ATmega644 ATmega645 ATmega1280 ATmega1281 ATmega1284 ATmega2560 ATmega2561 ATmega3250 ATmega6450

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ATMEGA32-16AU数据手册

Page:

of 27 Go

若手册格式错乱,请下载阅览PDF原文件

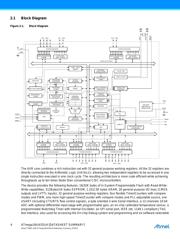

Atmel-7766IS-USB-ATmega16U4/32U4-Datasheet_Summary_072015

Features

• High Performance, Low Power AVR

®

8-Bit Microcontroller

• Advanced RISC Architecture

– 135 Powerful Instructions – Most Single Clock Cycle Execution

– 32 x 8 General Purpose Working Registers

– Fully Static Operation

– Up to 16 MIPS Throughput at 16MHz

– On-Chip 2-cycle Multiplier

• Non-volatile Program and Data Memories

– 16/32KB of In-System Self-Programmable Flash

– 1.25/2.5KB Internal SRAM

– 512Bytes/1KB Internal EEPROM

– Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

– Data retention: 20 years at 85C/ 100 years at 25C

(1)

– Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program

True Read-While-Write Operation

Parts using external XTAL clock are pre-programed with a default USB bootloader

– Programming Lock for Software Security

• JTAG (IEEE

®

std. 1149.1 compliant) Interface

– Boundary-scan Capabilities According to the JTAG Standard

– Extensive On-chip Debug Support

– Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

• USB 2.0 Full-speed/Low Speed Device Module with Interrupt on Transfer Completion

– Complies fully with Universal Serial Bus Specification Rev 2.0

– Supports data transfer rates up to 12Mbit/s and 1.5Mbit/s

– Endpoint 0 for Control Transfers: up to 64-bytes

– Six Programmable Endpoints with IN or Out Directions and with Bulk, Interrupt or

Isochronous Transfers

– Configurable Endpoints size up to 256 bytes in double bank mode

– Fully independent 832 bytes USB DPRAM for endpoint memory allocation

– Suspend/Resume Interrupts

– CPU Reset possible on USB Bus Reset detection

– 48MHz from PLL for Full-speed Bus Operation

– USB Bus Connection/Disconnection on Microcontroller Request

– Crystal-less operation for Low Speed mode

• Peripheral Features

– On-chip PLL for USB and High Speed Timer: 32 up to 96MHz operation

– One 8-bit Timer/Counter with Separate Prescaler and Compare Mode

ATmega16U4/ATmega32U4

8-bit Microcontroller with 16/32K bytes of ISP Flash and

USB Controller

DATASHEET SUMMARY

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件