Datasheet 搜索 > 微控制器 > Microchip(微芯) > ATMEGA32U4RC-MUR 数据手册 > ATMEGA32U4RC-MUR 用户编程技术手册 6/413 页

器件3D模型

器件3D模型¥ 13.661

ATMEGA32U4RC-MUR 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-44

描述:

8位微控制器 -MCU AVR USB 16K FL 16MHz Ind Temp Grn

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P5P62P138P139P142P144P147Hot

典型应用电路图在P240

原理图在P4P9P60P85P86P87P89P102P107P108P110P111

型号编码规则在P395P396P403

封装信息在P397

技术参数、封装参数在P358

应用领域在P37P46P58P59P314P317P329P330P412

电气规格在P60P239P358P403

导航目录

ATMEGA32U4RC-MUR数据手册

Page:

of 413 Go

若手册格式错乱,请下载阅览PDF原文件

6

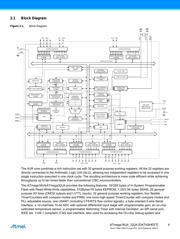

ATmega16U4_32U4 [DATASHEET]

Atmel-7766H-USB-ATmega16U4_32U4-Datasheet_092014

that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-

stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16U4/ATmega32U4 as listed on

page 71.

2.2.6 Port E (PE6,PE2)

Port E is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output

buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins

that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-

stated when a reset condition becomes active, even if the clock is not running.

Only bits 2 and 6 are present on the product pinout.

Port E also serves the functions of various special features of the ATmega16U4/ATmega32U4 as listed on

page 73.

2.2.7 Port F (PF7..PF4, PF1,PF0)

Port F serves as analog inputs to the A/D Converter.

Port F also serves as an 8-bit bi-directional I/O port, if the A/D Converter channels are not used. Port pins can

provide internal pull-up resistors (selected for each bit). The Port F output buffers have symmetrical drive

characteristics with both high sink and source capability. As inputs, Port F pins that are externally pulled low will

source current if the pull-up resistors are activated. The Port F pins are tri-stated when a reset condition

becomes active, even if the clock is not running.

Bits 2 and 3 are not present on the product pinout.

Port F also serves the functions of the JTAG interface. If the JTAG interface is enabled, the pull-up resistors on

pins PF7(TDI), PF5(TMS), and PF4(TCK) will be activated even if a reset occurs.

2.2.8 D-

USB Full speed / Low Speed Negative Data Upstream Port. Should be connected to the USB D- connector pin

with a serial 22Ω resistor.

2.2.9 D+

USB Full speed / Low Speed Positive Data Upstream Port. Should be connected to the USB D+ connector pin

with a serial 22Ω resistor.

2.2.10 UGND

USB Pads Ground.

2.2.11 UVCC

USB Pads Internal Regulator Input supply voltage.

2.2.12 UCAP

USB Pads Internal Regulator Output supply voltage. Should be connected to an external capacitor (1µF).

2.2.13 VBUS

USB VBUS monitor input.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件