Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > ATTINY2313A-MU 数据手册 > ATTINY2313A-MU 用户编程技术手册 3/274 页

器件3D模型

器件3D模型¥ 4.151

ATTINY2313A-MU 用户编程技术手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

QFN-20

描述:

8 位 PicoPower tinyAVR® 微控制器,AtmelAtmel 的 tinyAVR® 设备经优化处理,适用于需要性能、电源效率、易于使用且采用小型封装的应用。 所有 picoPower 设备均经过重新设计,旨在提供最低的功耗。最紧凑的小型封装,适用于注重尺寸的应用 电容式触摸 快速,且代码高效 高集成 1.8V 至 5.5V 操作(0.7V 操作,用于 ATtiny43U) ### AVR 微控制器,Atmel

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P2P3P57Hot

典型应用电路图在P162

原理图在P5P8P55P71P72P74P75P89P91P93P95P97

封装尺寸在P261P263P264

型号编码规则在P259P260P267

封装信息在P261

功能描述在P157

应用领域在P33

电气规格在P170

导航目录

ATTINY2313A-MU数据手册

Page:

of 274 Go

若手册格式错乱,请下载阅览PDF原文件

3

8246B–AVR–09/11

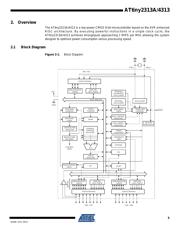

ATtiny2313A/4313

1.1 Pin Descriptions

1.1.1 VCC

Digital supply voltage.

1.1.2 GND

Ground.

1.1.3 Port A (PA2..PA0)

Port A is a 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port A output buffers have symmetrical drive characteristics with both high sink and source

capability, except PA2 which has the RESET

capability. To use pin PA2 as I/O pin, instead of

RESET pin, program (“0”) RSTDISBL fuse. As inputs, Port A pins that are externally pulled low

will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a

reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATtiny2313A/4313 as listed on

page 62.

1.1.4 Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port B output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port B pins are tri-stated when a reset condition becomes active,

even if the clock is not running.

Port B also serves the functions of various special features of the ATtiny2313A/4313 as listed on

page 63.

1.1.5 Port D (PD6..PD0)

Port D is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The

Port D output buffers have symmetrical drive characteristics with both high sink and source

capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up

resistors are activated. The Port D pins are tri-stated when a reset condition becomes active,

even if the clock is not running.

Port D also serves the functions of various special features of the ATtiny2313A/4313 as listed on

page 67.

1.1.6 RESET

Reset input. A low level on this pin for longer than the minimum pulse length will generate a

reset, even if the clock is not running and provided that the reset pin has not been disabled. The

minimum pulse length is given in Table 22-3 on page 201. Shorter pulses are not guaranteed to

generate a reset. The Reset Input is an alternate function for PA2 and dW.

The reset pin can also be used as a (weak) I/O pin.

1.1.7 XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit. XTAL1

is an alternate function for PA0.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件