Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > ATTINY85-20MUR 数据手册 > ATTINY85-20MUR 用户编程技术手册 2/235 页

¥ 6.714

ATTINY85-20MUR 用户编程技术手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

MLF-20

描述:

ATtiny 系列 8 KB 闪存 512 B SRAM 20 MHz 8-位 微控制器 - MLF-20

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P2P55Hot

典型应用电路图在P114

原理图在P4P7P53P65P68P69P71P84P85P96P97P108

封装尺寸在P207P208P209P210P211P218

型号编码规则在P204P205P206P220P221

封装信息在P207

功能描述在P109

应用领域在P32

电气规格在P53P139P220

导航目录

ATTINY85-20MUR数据手册

Page:

of 235 Go

若手册格式错乱,请下载阅览PDF原文件

2

ATtiny25/45/85 [DATASHEET]

2586Q–AVR–08/2013

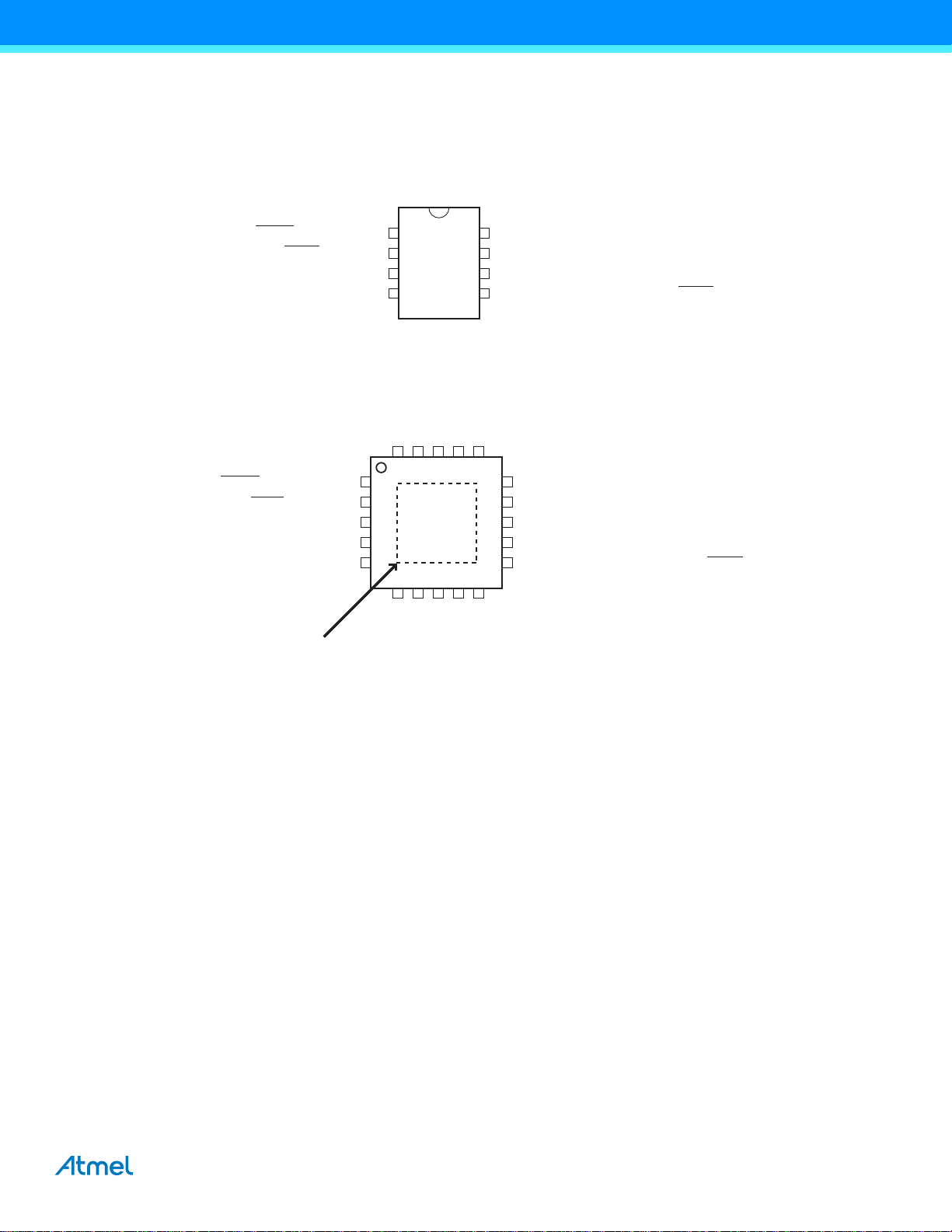

1. Pin Configurations

Figure 1-1. Pinout ATtiny25/45/85

1.1 Pin Descriptions

1.1.1 VCC

Supply voltage.

1.1.2 GND

Ground.

1.1.3 Port B (PB5:PB0)

Port B is a 6-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers

have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are

externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a

reset condition becomes active, even if the clock is not running.

1

2

3

4

8

7

6

5

(PCINT5/RESET/ADC0/dW) PB5

(PCINT3/XTAL1/CLKI/OC1B/ADC3) PB3

(PCINT4/XTAL2/CLKO/OC1B/ADC2) PB4

GND

VCC

PB2 (SCK/USCK/SCL/ADC1/T0/INT0/PCINT2)

PB1 (MISO/DO/AIN1/OC0B/OC1A/PCINT1)

PB0 (MOSI/DI/SDA/AIN0/OC0A/OC1A/AREF/PCINT0)

PDIP/SOIC/TSSOP

1

2

3

4

5

QFN/MLF

15

14

13

12

11

20

19

18

17

16

6

7

8

9

10

DNC

DNC

GND

DNC

DNC

DNC

DNC

DNC

DNC

DNC

NOTE: Bottom pad should be soldered to ground.

DNC: Do Not Connect

NOTE: TSSOP only for ATtiny45/V

(PCINT5/RESET/ADC0/dW) PB5

(PCINT3/XTAL1/CLKI/OC1B/ADC3) PB3

DNC

DNC

(PCINT4/XTAL2/CLKO/OC1B/ADC2) PB4

VCC

PB2 (SCK/USCK/SCL/ADC1/T0/INT0/PCINT2)

DNC

PB1 (MISO/DO/AIN1/OC0B/OC1A/PCINT1)

PB0 (MOSI/DI/SDA/AIN0/OC0A/OC1A/AREF/PCINT0)

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件