Datasheet 搜索 > LVDS、M-LVDS、ECL、CML > TI(德州仪器) > DS90C385AMT 数据手册 > DS90C385AMT 用户编程技术手册 1/17 页

器件3D模型

器件3D模型¥ 29.504

DS90C385AMT 用户编程技术手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

LVDS、M-LVDS、ECL、CML

封装:

TSSOP-56

描述:

TEXAS INSTRUMENTS DS90C385AMT 驱动器, LVDS, 收发器, 0 °C, 150 °C, 3 V

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P11P12P13P14Hot

典型应用电路图在P15

原理图在P1

封装尺寸在P16P17

焊接温度在P2

功能描述在P1

技术参数、封装参数在P2P3

应用领域在P11P12P14P15

电气规格在P2P3

导航目录

DS90C385AMT数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

DS90C385/DS90C365

+3.3V Programmable LVDS Transmitter 24-Bit Flat Panel

Display (FPD) Link-85 MHz, +3.3V Programmable LVDS

Transmitter 18-Bit Flat Panel Display (FPD) Link-85 MHz

General Description

The DS90C385 transmitter converts 28 bits of LVCMOS/

LVTTL data into four LVDS (Low Voltage Differential Signal-

ing) data streams. A phase-locked transmit clock is transmit-

ted in parallel with the data streams over a fifth LVDS link.

Every cycle of the transmit clock 28 bits of input data are

sampled and transmitted. At a transmit clock frequency of 85

MHz, 24 bits of RGB data and 3 bits of LCD timing and

control data (FPLINE, FPFRAME, DRDY) are transmitted at

a rate of 595 Mbps per LVDS data channel. Using a 85 MHz

clock, the data throughput is 297.5 Mbytes/sec. Also avail-

able is the DS90C365 that converts 21 bits of LVCMOS/

LVTTL data into three LVDS (Low Voltage Differential Sig-

naling) data streams. Both transmitters can be programmed

for Rising edge strobe or Falling edge strobe through a

dedicated pin. A Rising edge or Falling edge strobe transmit-

ter will interoperate with a Falling edge strobe Receiver

(DS90CF386/DS90CF366) without any translation logic.

The DS90C385 is also offered in a 64 ball, 0.8mm fine pitch

ball grid array (FBGA) package which provides a 44 %

reduction in PCB footprint compared to the TSSOP package.

This chipset is an ideal means to solve EMI and cable size

problems associated with wide, high-speed TTL interfaces.

Features

n 20 to 85 MHz shift clock support

n Best–in–Class Set & Hold Times on TxINPUTs

n Tx power consumption

<

130 mW (typ)

@

85MHz

Grayscale

n Tx Power-down mode

<

200µW (max)

n Supports VGA, SVGA, XGA and Dual Pixel SXGA.

n Narrow bus reduces cable size and cost

n Up to 2.38 Gbps throughput

n Up to 297.5 Megabytes/sec bandwidth

n 345 mV (typ) swing LVDS devices for low EMI

n PLL requires no external components

n Compatible with TIA/EIA-644 LVDS standard

n Low profile 56-lead or 48-lead TSSOP package

n DS90C385 also available in a 64 ball, 0.8mm fine pitch

ball grid array (FBGA) package

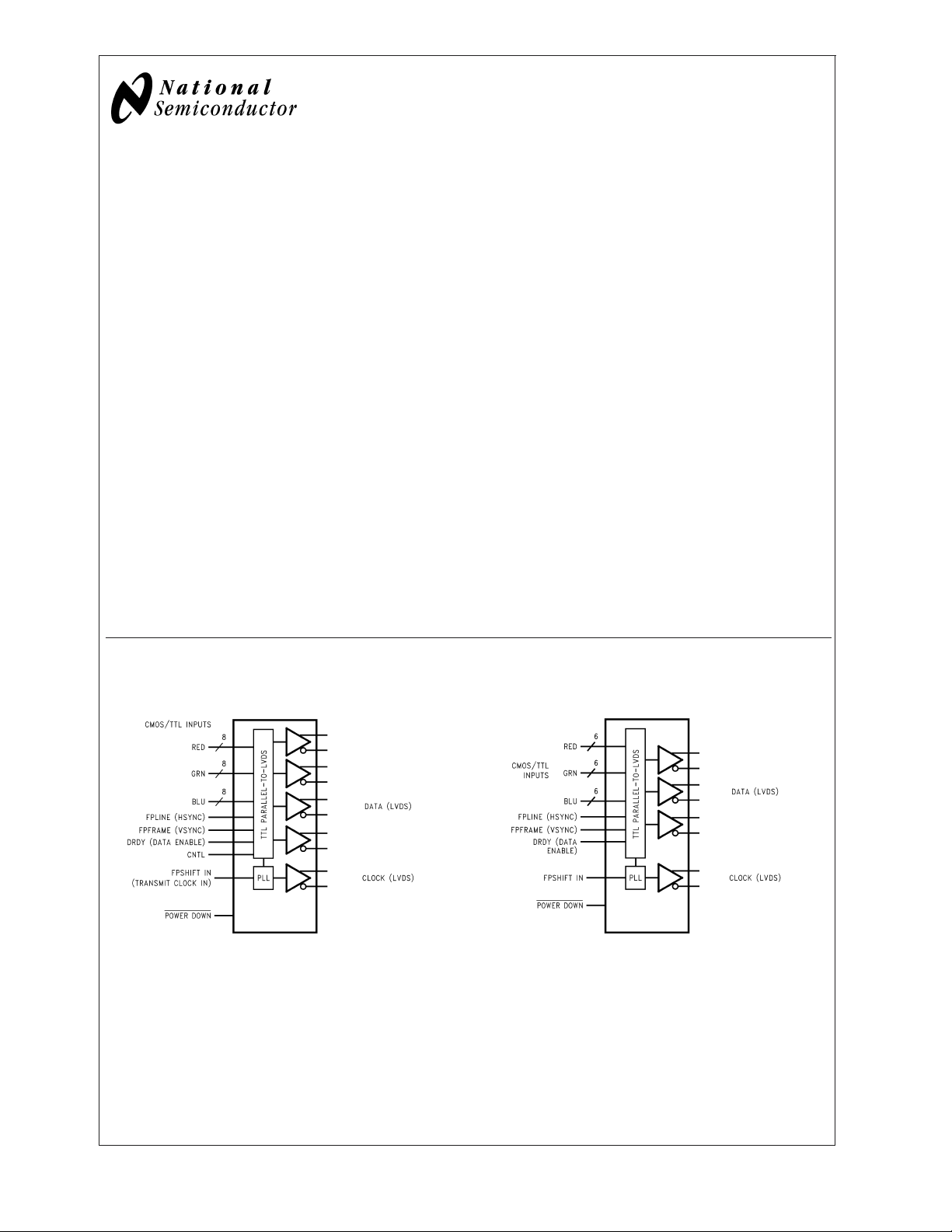

Block Diagrams

DS90C385

10086801

Order Number DS90C385MTD or DS90C385SLC

See NS Package Number MTD56 or SLC64A

DS90C365

10086829

Order Number DS90C365MTD

See NS Package Number MTD48

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

May 2003

DS90C385/DS90C365 +3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display (FPD)

Link-85 MHz, +3.3V Programmable LVDS Transmitter 18-Bit Flat Panel Display (FPD) Link-85 MHz

© 2003 National Semiconductor Corporation DS100868 www.national.com

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件