Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EPF10K50SQC208-3N 数据手册 > EPF10K50SQC208-3N 用户编程技术手册 1/100 页

器件3D模型

器件3D模型¥ 240.567

EPF10K50SQC208-3N 用户编程技术手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

QFP-208

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

EPF10K50SQC208-3N数据手册

Page:

of 100 Go

若手册格式错乱,请下载阅览PDF原文件

Altera Corporation 1

FLEX 10KE

Embedded Programmable

Logic Device

January 2003, ver. 2.5 Data Sheet

DS-F10KE-2.5

®

Features...

■ Embedded programmable logic devices (PLDs), providing

system-on-a-programmable-chip (SOPC) integration in a single

device

– Enhanced embedded array for implementing megafunctions

such as efficient memory and specialized logic functions

– Dual-port capability with up to 16-bit width per embedded array

block (EAB)

– Logic array for general logic functions

■ High density

– 30,000 to 200,000 typical gates (see Tables 1 and 2)

– Up to 98,304 RAM bits (4,096 bits per EAB), all of which can be

used without reducing logic capacity

■ System-level features

– MultiVolt

TM

I/O pins can drive or be driven by 2.5-V, 3.3-V, or

5.0-V devices

– Low power consumption

– Bidirectional I/O performance (t

SU

and t

CO

) up to 212 MHz

– Fully compliant with the PCI Special Interest Group (PCI SIG)

PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at

33 MHz or 66 MHz

– -1 speed grade devices are compliant with PCI Local Bus

Specification, Revision 2.2, for 5.0-V operation

– Built-in Joint Test Action Group (JTAG) boundary-scan test

(BST) circuitry compliant with IEEE Std. 1149.1-1990, available

without consuming additional device logic

f

For information on 5.0-V FLEX

®

10K or 3.3-V FLEX 10KA devices, see the

FLEX 10K Embedded Programmable Logic Family Data Sheet.

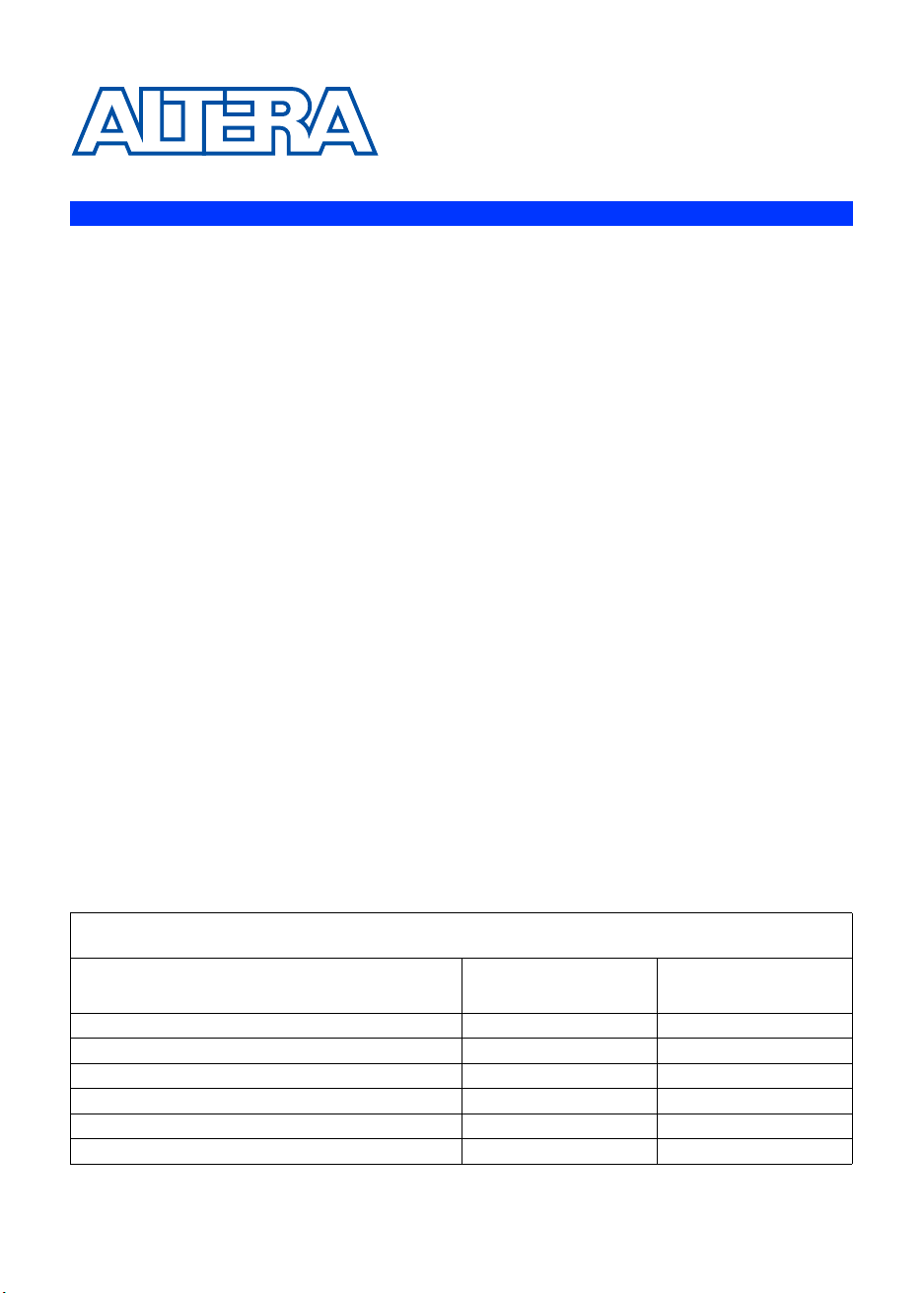

Table 1. FLEX 10KE Device Features

Feature EPF10K30E EPF10K50E

EPF10K50S

Typical gates (1) 30,000 50,000

Maximum system gates 119,000 199,000

Logic elements (LEs) 1,728 2,880

EABs 6 10

Total RAM bits 24,576 40,960

Maximum user I/O pins 220 254

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件