Datasheet 搜索 > CPLD芯片 > Altera(阿尔特拉) > EPM7064SLC44-10F 数据手册 > EPM7064SLC44-10F 用户编程技术手册 1/66 页

器件3D模型

器件3D模型¥ 0

EPM7064SLC44-10F 用户编程技术手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

CPLD芯片

封装:

PLCC-44

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

EPM7064SLC44-10F数据手册

Page:

of 66 Go

若手册格式错乱,请下载阅览PDF原文件

®

Altera Corporation 1

MAX 7000

Programmable Logic

Device Family

September 2005, ver. 6.7 Data Sheet

DS-MAX7000-6.7

Features...

■ High-performance, EEPROM-based programmable logic devices

(PLDs) based on second-generation MAX

®

architecture

■ 5.0-V in-system programmability (ISP) through the built-in

IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface available in

MAX 7000S devices

– ISP circuitry compatible with IEEE Std. 1532

■ Includes 5.0-V MAX 7000 devices and 5.0-V ISP-based MAX 7000S

devices

■ Built-in JTAG boundary-scan test (BST) circuitry in MAX

7000S

devices with 128 or more macrocells

■ Complete EPLD family with logic densities ranging from 600 to

5,000 usable gates (see Tables 1 and 2)

■ 5-ns pin-to-pin logic delays with up to 175.4-MHz counter

frequencies (including interconnect)

■ PCI-compliant devices available

f

For information on in-system programmable 3.3-V MAX 7000A or 2.5-V

MAX 7000B devices, see the MAX 7000A Programmable Logic Device Family

Data Sheet or the MAX 7000B Programmable Logic Device Family Data

Sheet.

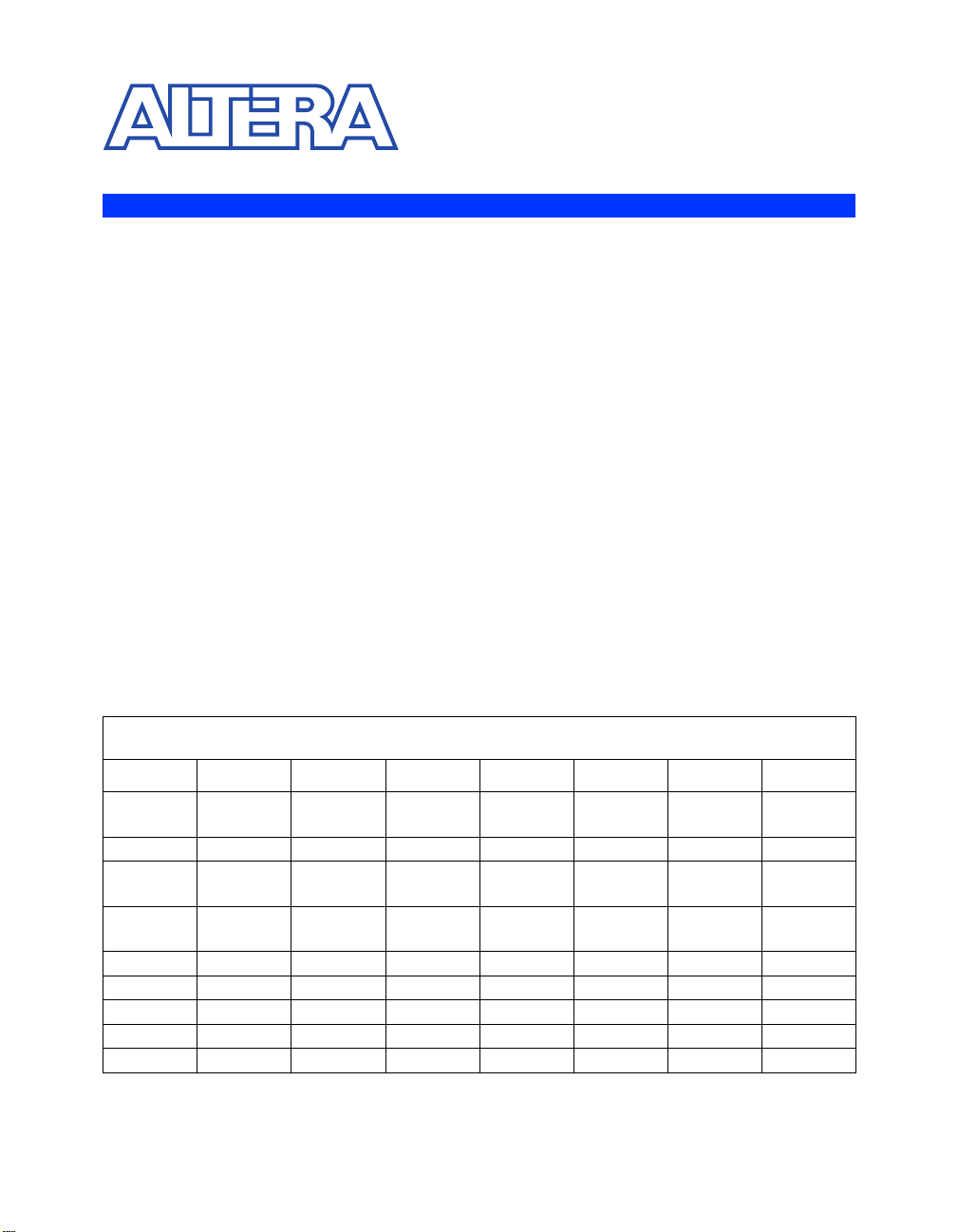

Table 1. MAX 7000 Device Features

Feature EPM7032 EPM7064 EPM7096 EPM7128E EPM7160E EPM7192E EPM7256E

Usable

gates

600 1,250 1,800 2,500 3,200 3,750 5,000

Macrocells 32 64 96 128 160 192 256

Logic array

blocks

2468101216

Maximum

user I/O pins

36 68 76 100 104 124 164

t

PD

(ns) 6 6 7.5 7.5 10 12 12

t

SU

(ns)5566777

t

FSU

(ns)2.5 2.533333

t

CO1

(ns) 4 4 4.5 4.5 5 6 6

f

CNT

(MHz) 151.5 151.5 125.0 125.0 100.0 90.9 90.9

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件