Datasheet 搜索 > 时钟发生器 > Hittite > HMC988LP3E 数据手册 > HMC988LP3E 用户编程技术手册 1/22 页

¥ 100.058

HMC988LP3E 用户编程技术手册 - Hittite

制造商:

Hittite

分类:

时钟发生器

封装:

VFQFN-16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P6Hot

典型应用电路图在P1P11P14P15

原理图在P9

封装尺寸在P8

标记信息在P8

功能描述在P1P6

技术参数、封装参数在P1P2P3P4P5P6P7P8P9P11P12P13

应用领域在P1

电气规格在P4

导航目录

HMC988LP3E数据手册

Page:

of 22 Go

若手册格式错乱,请下载阅览PDF原文件

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824

Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at www.hittite.com

Application Support: Phone: 978-250-3343 or apps@hittite.com

CLOCK DISTRIBUTION - SMT

1

HMC988LP3E

v04.1014

PROGRAMMABLE CLOCK DIVIDER AND DELAY

DC - 4 GHz

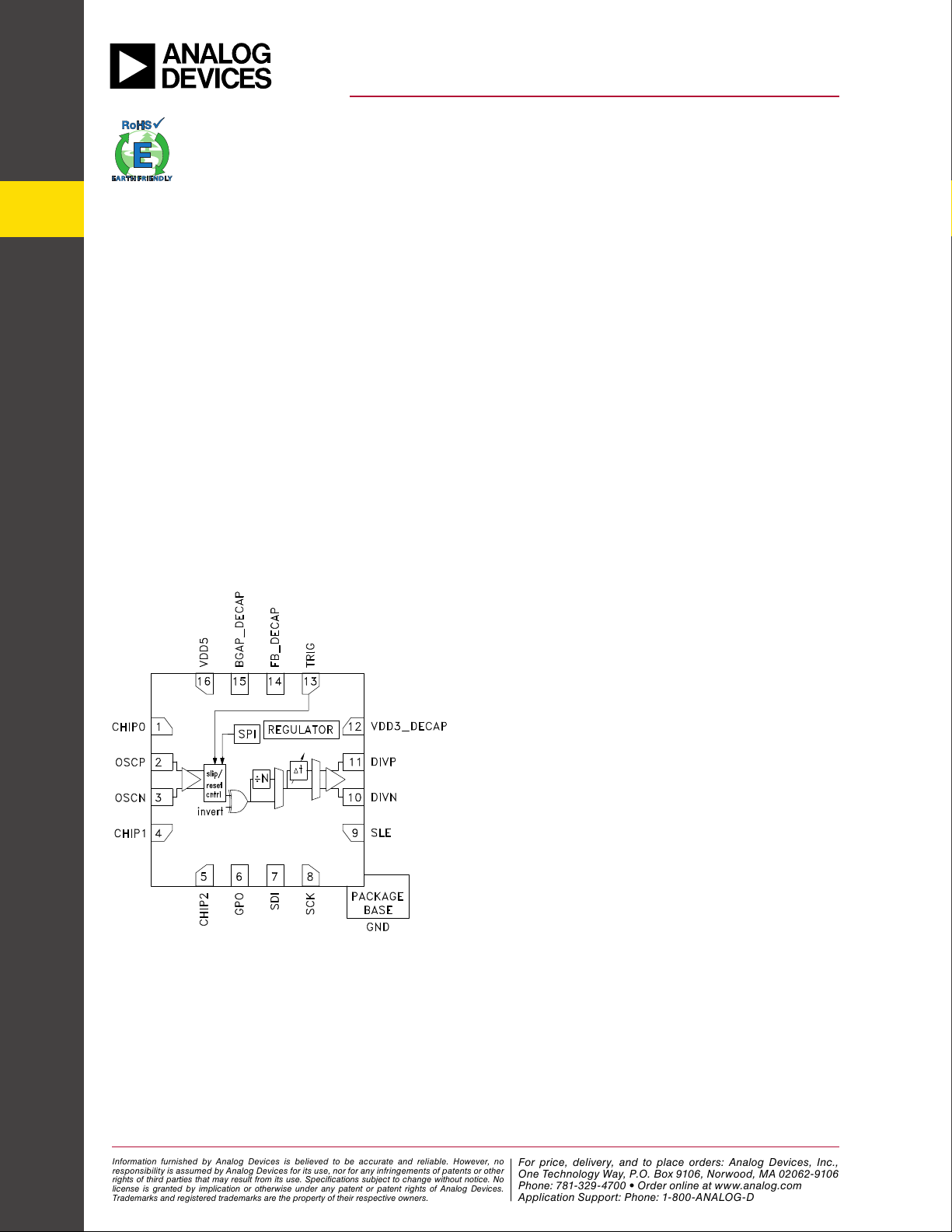

Functional Diagram

Typical Applications Features

General Description

The HMC988LP3E is ideal for:

• Basestation Digital Pre-Distortion Paths(DPD)

• High Performance Automated Test

Equipment(ATE)

• Backplane clock skew management

• Phase Coherence of multiple clock paths

• Clock Delay management to improve setup &

hold time margins

•

PCB signal ight time offset circuits

• Track and hold circuits for ADC/DACs

DC - 4 GHz

-170 dBc/Hz oor @ 100 MHz output

-164 dBc/Hz oor @ 2 GHz output

Integrated Jitter 35 fs

RMS

@ 100 MHz output

13 fs

RMS

(calculated) @ 2 GHz output

Adjustable output phase with soft/hard reset sync

Adjustable output delay in 60 steps of 20 ps

Flexible Input Interface:

LVPECL,LVDS,CML,CMOS Compatible

AC or DC Coupling

On - Chip Termination 50 Ω (100 Ω Differential)

Output Driver (LVPECL):

800 mVpp LVPECL into 50 Ω Single-Ended (+3

dBm Fo)

Up to 8 addressable dividers per SPI bus

3.3 V operation or 5 V operation with Optional on-

chip regulator for best performance

3 x 3 QFN Leadless SMT Package

The HMC988LP3E is a an ultra low noise clock

divider capable of dividing by 1/2/4/8/16/32. It is a

versatile device with additional functionality including

adjustable output phase, adjustable delay in 60 steps

of ~ 20 ps, a clock synchronization function, and a

clock invert option.

Housed in a compact 3x3 mm SMT QFN package, the

clock divider offers a high level of functionality. The

device works with 3.3 V supply or may be connected

to 5 V supply and utilize the optional on-chip regulator.

This on-chip regulator may be bypassed.

Up to 8 addressable HMC988LP3E devices can be

used together on the SPI bus.

The HMC988LP3E is ideally suited for data converter

applications with extremely low phase noise

requirements.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc.,

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106

Phone: 781-329-4700 • Order online at www.analog.com

Application Support: Phone: 1-800-ANALOG-D

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件