Datasheet 搜索 > 开发套件 > TI(德州仪器) > LMK61E2EVM 数据手册 > LMK61E2EVM 用户编程技术手册 1/55 页

¥ 710.8

LMK61E2EVM 用户编程技术手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

开发套件

描述:

TEXAS INSTRUMENTS LMK61E2EVM 评估电路板, LMK61E2, 可编程振荡器

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3Hot

典型应用电路图在P37P38P39P40P41P42P43

原理图在P1P14

封装尺寸在P48P50P51P52

焊盘布局在P45P53

标记信息在P48

封装信息在P47P48P49P50P51

焊接温度在P44

技术参数、封装参数在P3

应用领域在P1P37P38P39P40P41P42P43

电气规格在P4

导航目录

LMK61E2EVM数据手册

Page:

of 55 Go

若手册格式错乱,请下载阅览PDF原文件

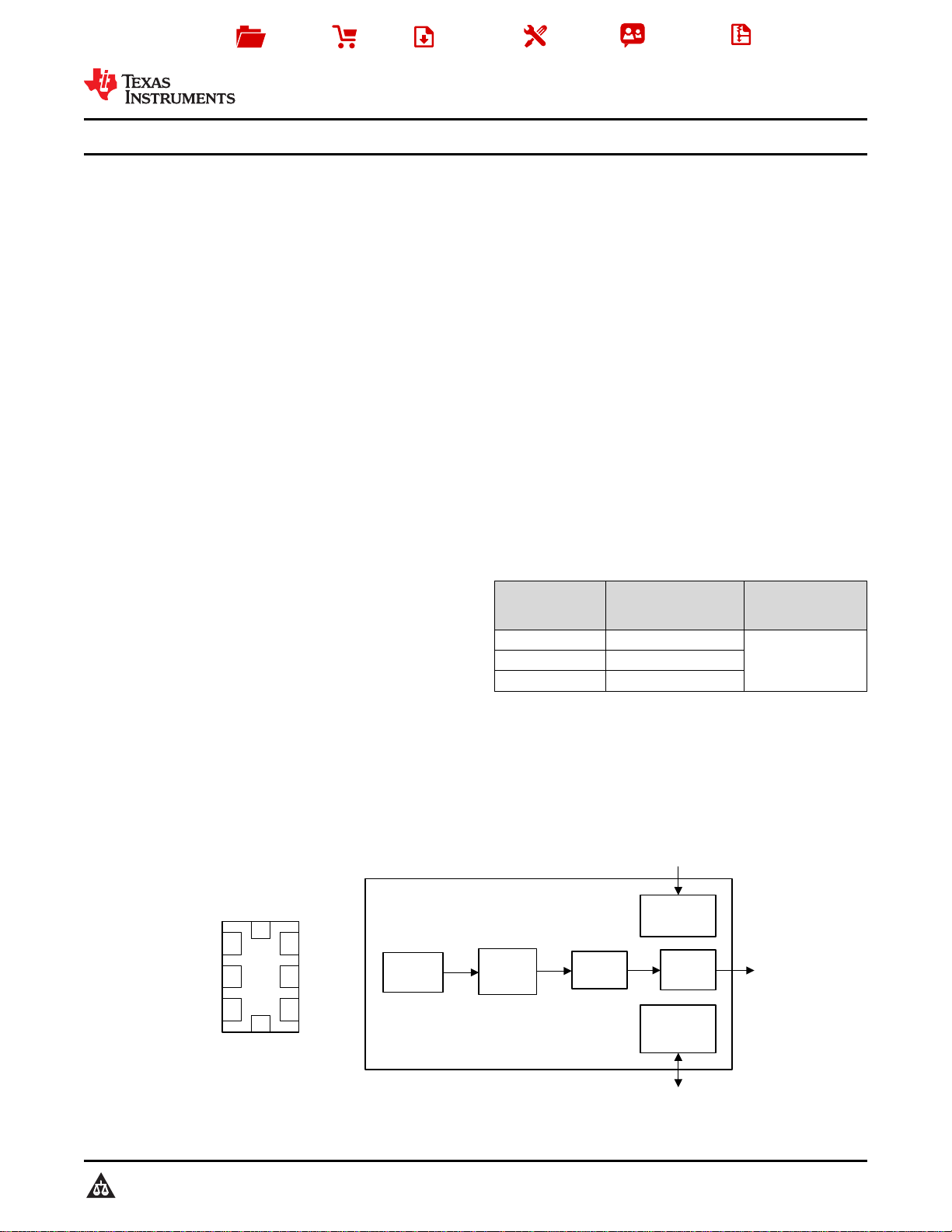

ADD OUTN

VDDOE

GND OUTP

SCL

SDA

1 6

2 5

43

7

8

LMK61E2

Ultra-high performance oscillator

PLL

Output

Divider

Output

Buffer

Power

Conditioning

Interface

I

2

C/EEPROM

Integrated

Oscillator

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

Reference

Design

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

LMK61E2

SNAS674B –SEPTEMBER 2015–REVISED FEBRUARY 2017

LMK61E2 Ultra-Low Jitter Programmable Oscillator With Internal EEPROM

1

1 Features

1

• Ultra-Low Noise, High Performance

– Jitter: 90 fs RMS Typical f

OUT

> 100 MHz

– PSRR: –70 dBc, Robust Supply Noise

Immunity

• Flexible Output Format; User Selectable

– LVPECL up to 1 GHz

– LVDS up to 900 MHz

– HCSL up to 400 MHz

• Total Frequency Tolerance of ±50 ppm

• System Level Features

– Frequency Margining: Fine and Coarse

– Internal EEPROM: User Configurable Default

Settings

• Other Features

– Device Control: I

2

C

– 3.3-V Operating Voltage

– Industrial Temperature Range (–40ºC to

+85ºC)

– 7-mm × 5-mm 8-Pin Package

– Create a Custom Design Using the LMK61E2

With the WEBENCH

®

Power Designer

2 Applications

• High-Performance Replacement for Crystal-,

SAW-, or Silicon-Based Oscillators

• Switches, Routers, Network Line Cards, Base

Band Units (BBU), Servers, Storage/SAN

• Test and Measurement

• Medical Imaging

• FPGA, Processor Attach

3 Description

The LMK61E2 device is an ultra-low jitter

PLLatinum™ programmable oscillator with a

fractional-N frequency synthesizer with integrated

VCO that generates commonly used reference

clocks. The outputs can be configured as LVPECL,

LVDS, or HCSL.

The device features self start-up from on-chip

EEPROM that is factory programmed to generate

156.25-MHz LVPECL output. The device registers

and EEPROM settings are fully programmable in-

system through I

2

C serial interface. Internal power

conditioning provide excellent power supply ripple

rejection (PSRR), reducing the cost and complexity of

the power delivery network. The device operates from

a single 3.3-V ± 5% supply.

The device provides fine and coarse frequency

margining options through I

2

C serial interface to

support system design verification tests (DVT), such

as standard compliance and system timing margin

testing.

Device Information

(1)

PART NUMBER

DEFAULT OUTPUT

FREQ (MHz) AND

FORMAT

PACKAGE AND

BODY SIZE (NOM)

LMK61E2 156.25 LVPECL

8-pin QFM (SIA),

7.00 mm x 5.00 mm

LMK61E2BAA 156.25 LVDS

LMK61E2BBA 125 LVDS

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Pinout and Simplified Block Diagram

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件