Datasheet 搜索 > 热敏电阻 > VISHAY(威世) > NTCS0603E3104FXT 数据手册 > NTCS0603E3104FXT 用户编程技术手册 1/6 页

器件3D模型

器件3D模型¥ 1.051

NTCS0603E3104FXT 用户编程技术手册 - VISHAY(威世)

制造商:

VISHAY(威世)

分类:

热敏电阻

封装:

0603

描述:

0603贴片,玻璃保护的NTC热敏电阻 SMD 0603, Glass Protected NTC Thermistors

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

应用领域在P6

导航目录

NTCS0603E3104FXT数据手册

Page:

of 6 Go

若手册格式错乱,请下载阅览PDF原文件

1 Controlling the AIC3104

2 Determining Sample Rate and Master Clock Frequency

Application Report

SLAA403 – February 2009

TLV320AIC3104 Programming Made Easy

David K. Wilson ............................................................................................. Audio Converter Products

ABSTRACT

The TLV320AIC3104 (AIC3104) is a versatile audio codec with multiple features. When

first designing with the AIC3104, reading the entire data sheet and becoming familiar

with the entire register set can be a daunting task. However, in many common

configurations, it is possible to get the AIC3104 up and running while only writing to as

few as 12 registers.

Although not intended to replace the data sheet, this document details several common

configurations for the AIC3104. It gives a concise description of how to set up the

codec and gives a script example that can be used to accelerate your design.

All features of the AIC3104 are accessed by programmable registers. The registers can be programmed

by an external microprocessor or DSP using I

2

C™ protocol. The master clock (MCLK) is not required to

be running while programming the AIC3104. The fixed 7-bit I

2

C address for the AIC3104 is 001 1000

(0x30h to write, 0x31h to read). The AIC3104 supports I

2

C data rates up to 400 kHz.

It is good practice to perform a hardware reset after initial power up to ensure that all registers are in their

default states and that the AIC3104 is ready to be programmed.

The first task for any design using the AIC3104 is to determine the desired sample rate and master clock

frequency. With the exception of register programming, all internal timing, including the sample rate, is

ultimately derived from an external master clock. By default, the ADC and DAC sample rates are

MCLK/256. For the common audio sample rates 44.1 ksps and 48 ksps, the most common MCLK

frequencies are 11.2896 MHz (44.1 ksps × 256) and 12.288 MHz (48 ksps × 256). If you are using one of

these two MCLK frequencies and sample rates, no register programming is needed to set the sample rate.

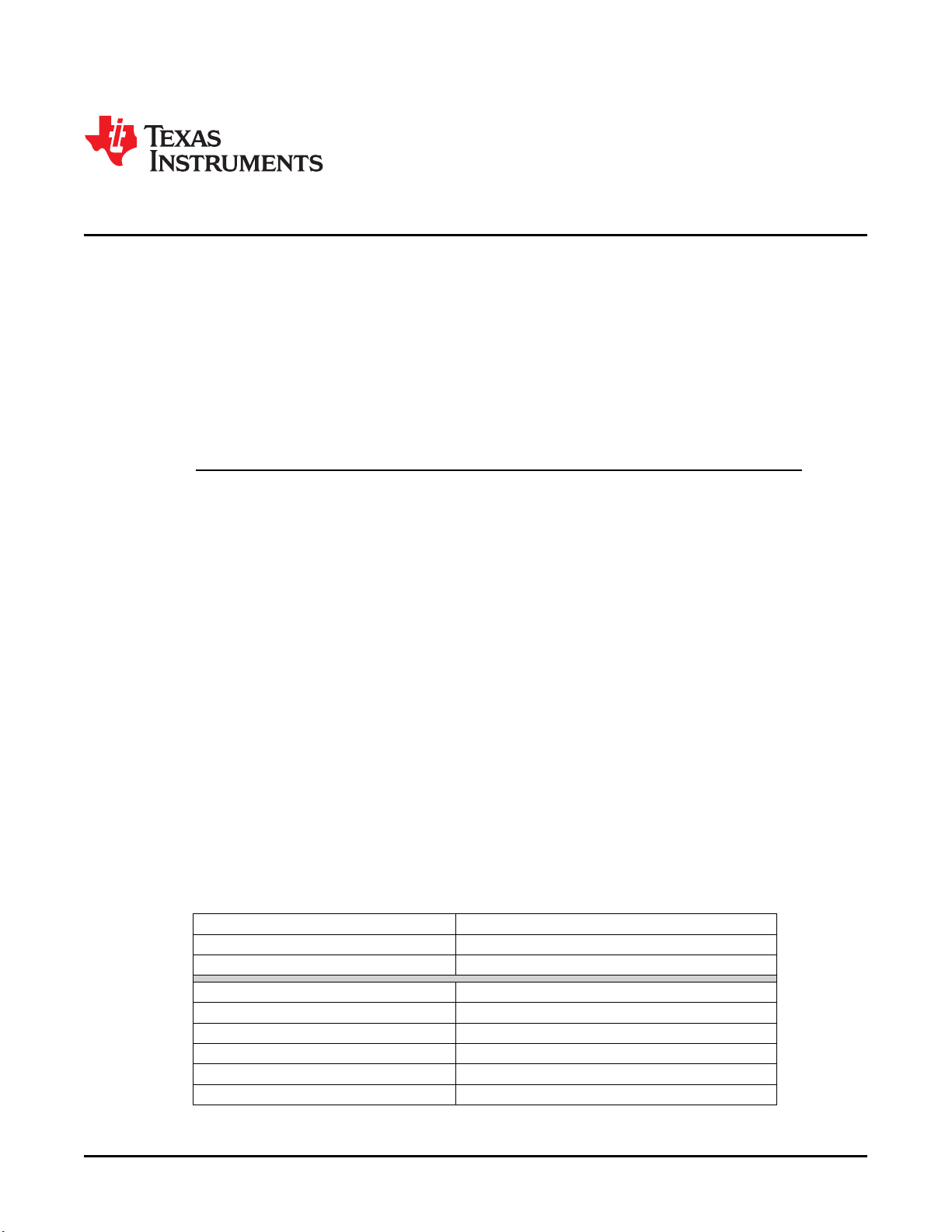

Table 1 shows two common audio MCLK frequencies and the settings required to obtain common sample

rates.

Table 1. MCLK Frequencies and Settings

DESIRED SAMPLE RATE REGISTER SETTINGS

MCLK = 11.2896 MHz

44.1 ksps None Required (use defaults)

MCLK = 12.288 MHz

48 ksps None Required (use defaults)

8 ksps Register 2, Page 0 = 0xAA

16 ksps Register 2, Page 0 = 0x44

32 ksps Register 2, Page 0 = 0x11

96 ksps Register 7, Page 0, D6 and D5 = 1

I

2

C is a trademark of Koninklijke Philips Electronics NV.

SLAA403 – February 2009 TLV320AIC3104 Programming Made Easy 1

Submit Documentation Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件