Datasheet 搜索 > 8位微控制器 > Microchip(微芯) > PIC16F1778-E/SP 数据手册 > PIC16F1778-E/SP 用户编程技术手册 2/16 页

器件3D模型

器件3D模型¥ 7.565

PIC16F1778-E/SP 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

8位微控制器

封装:

DIP-28

描述:

8位微控制器 -MCU 8-Bit MCU, 28K Flash 2KB RAM, 10b ADC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P1

应用领域在P10

导航目录

PIC16F1778-E/SP数据手册

Page:

of 16 Go

若手册格式错乱,请下载阅览PDF原文件

TB3140

DS90003140B-page 2 2016 Microchip Technology Inc.

INPUT TIMING SOURCES

The PRG combines two selectable independent timing

sources to generate control timing for its ramp output.

These sources can be an external input from the

PRGxR and PRGxF pins, or output/s from other

peripherals. The set rising input is selected by setting

the Set Rising Timing Source Select bits (RTSS<3:0>)

in the PRGxRTSS register while the set falling input is

selected by setting the Set Falling Timing Source

Select bits (FTSS<3:0>) in the PRGxFTSS register.

The polarity of timing sources is selected by setting the

Fall Event Polarity Select bit (FPOL) and the Rise

Event Polarity Select bit (RPOL) in the PRGxCON1

register.

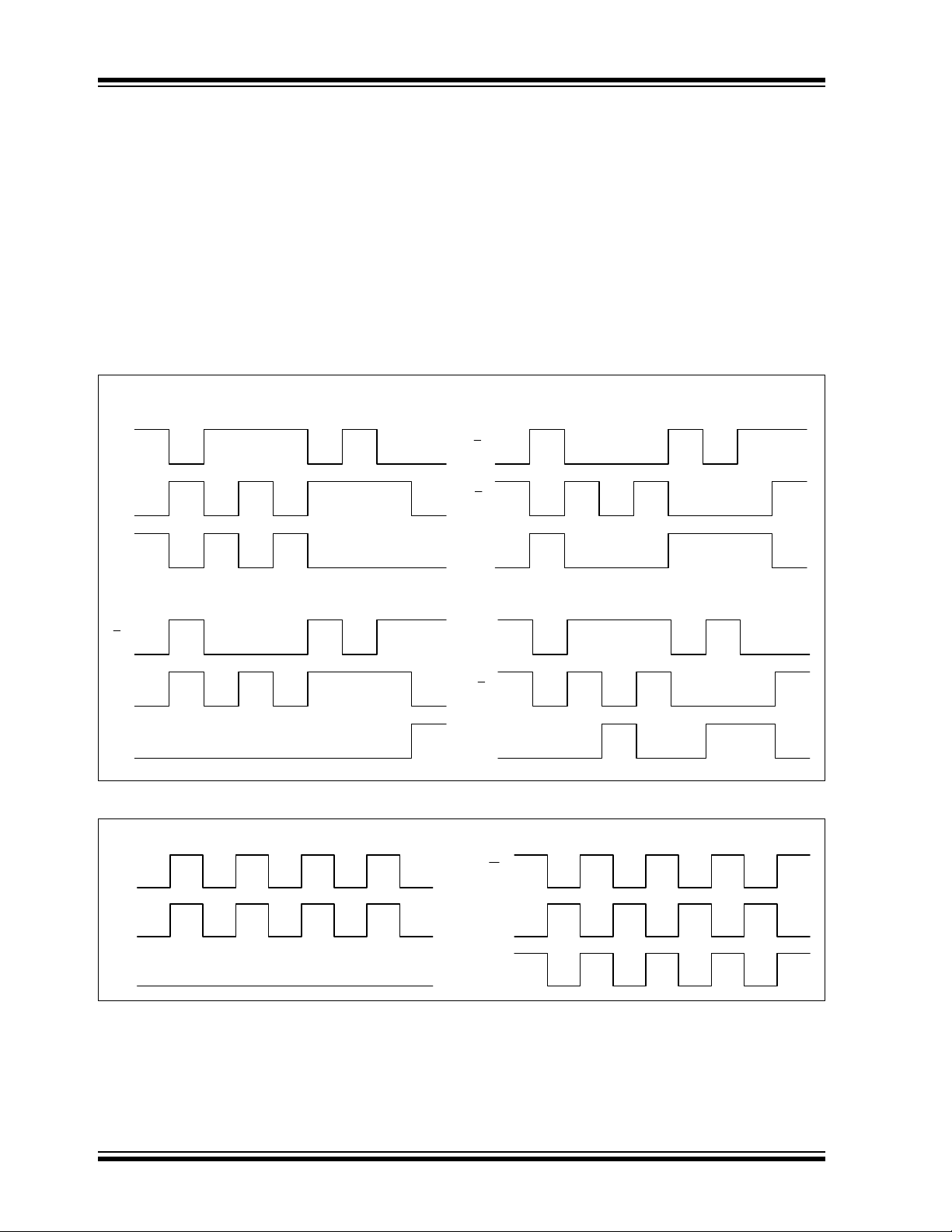

In Figure 2, when set rising input (S) is true and set

falling input is false (R), the PRG output timing (Q) is

true or vice versa. When both S and R are false, Q

retains its previous state. However, when both S and R

inputs are true, R dominates S and forces Q to False

state. This condition can be encountered when the

same source for both set rising and falling is used. To

control the operation with this condition, either of the

two timing inputs must be inverted. Otherwise, Q will

not produce a timing pulse as shown in Figure 3.

FIGURE 2: DIFFERENT INPUT SOURCES

FIGURE 3: SINGLE-ENDED INPUT SOURCE

S

R

Q

S

R

Q

RPOL =0; FPOL=0

RPOL =1; FPOL=0

S

R

Q

RPOL =1; FPOL=1

R

Q

S

RPOL =0; FPOL=1

R

Q

RPOL =1; FPOL=0

S

R

Q

RPOL =0; FPOL=0

S

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件