Datasheet 搜索 > 8位微控制器 > Microchip(微芯) > PIC16F505T-I/ST 数据手册 > PIC16F505T-I/ST 用户编程技术手册 4/22 页

器件3D模型

器件3D模型¥ 2.7

PIC16F505T-I/ST 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

8位微控制器

封装:

TSSOP-14

描述:

8月14日引脚, 8位闪存微控制器 8/14-Pin, 8-Bit Flash Microcontrollers

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P2Hot

电气规格在P18

导航目录

PIC16F505T-I/ST数据手册

Page:

of 22 Go

若手册格式错乱,请下载阅览PDF原文件

PIC16F505

DS41226G-page 4 Preliminary 2010 Microchip Technology Inc.

3.0 COMMANDS AND

ALGORITHMS

3.1 Program/Verify Mode

The Program/Verify mode is entered by holding pins

ICSPCLK and ICSPDAT low while raising V

DD pin from

V

IL to VDD. Then raise VPP from VIL to VIHH. Once in

this mode, the user program memory and configuration

memory can be accessed and programmed in serial

fashion. Clock and data are Schmitt Trigger input in this

mode (see Figure 3-1).

The sequence that enters the device into the

Programming/Verify mode places all other logic into the

Reset state (the MCLR

pin was initially at VIL). This

means that all I/O are in the Reset state (high-

impedance inputs).

3.1.1 PROGRAMMING

The programming sequence loads a word, programs,

verifies and finally increments the PC.

Program/Verify mode entry will set the address to

0x7FF. The Increment Address command will

increment the PC. The available commands are shown

in Table 3-1.

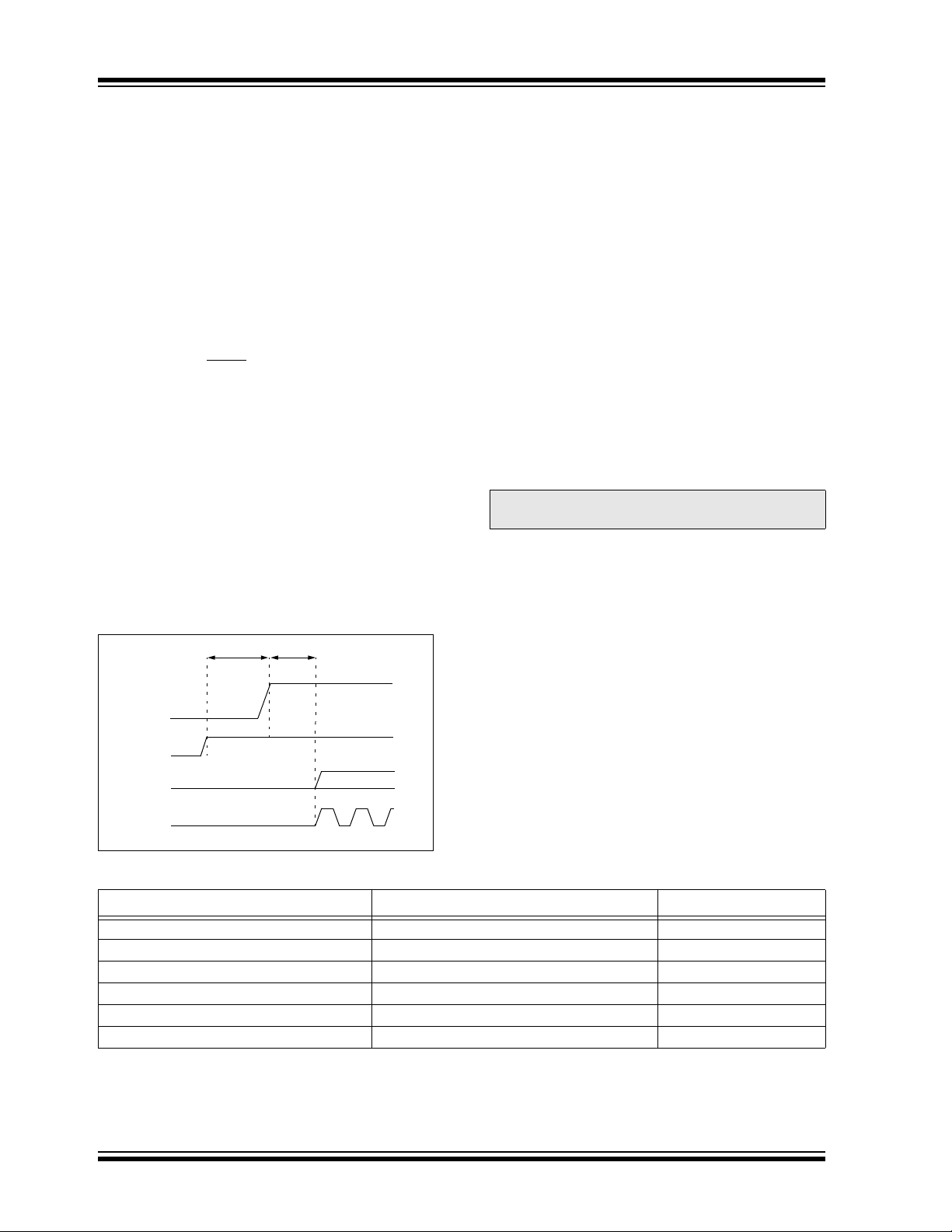

FIGURE 3-1: ENTERING HIGH

VOLTAGE PROGRAM/

VERIFY MODE

3.1.2 SERIAL PROGRAM/VERIFY

OPERATION

The ICSPCLK pin is used for clock input and the

ICSPDAT pin is used for data input/output during serial

operation. To input a command, the clock pin is cycled

six times. Each command bit is latched on the falling

edge of the clock with the LSb of the command being

input first. The data must adhere to the setup (T

SET1)

and hold (T

HLD1) times with respect to the falling edge

of the clock (see Table 6-1).

Commands that do not have data associated with them

are required to wait a minimum of T

DLY2 measured

from the falling edge of the last command clock to the

rising edge of the next command clock (see Table 6-1).

Commands that do have data associated with them

(Read and Load) are also required to wait TDLY2

between the command and the data segment

measured from the falling edge of the last command

clock to the rising edge of the first data clock. The data

segment, consisting of 16 clock cycles, can begin after

this delay.

The first and last clock pulses during the data segment

correspond to the Start and Stop bits, respectively.

Input data is a “don’t care” during the Start and Stop

cycles. The 14 clock pulses between the Start and Stop

cycles, clock the 14 bits of input/output data. Data is

transferred LSb first.

During Read commands, in which the data is output

from the PIC16F505, the ICSPDAT pin transitions from

the high-impedance input state to the low-impedance

output state at the rising edge of the second data clock

(first clock edge after the Start cycle). The ICSPDAT pin

returns to the high-impedance state at the rising edge

of the 16th data clock (first edge of the Stop cycle). See

Figure 3-3.

The commands that are available are described in

Table 3-1.

TABLE 3-1: COMMAND MAPPING FOR PIC16F505

VPP

THLD0

ICSPDAT

ICSPCLK

VDD

TPPDP

Note: After every End Programming command,

a delay of T

DIS must be delayed.

Command Mapping (MSb … LSb) Data

Load Data for Program Memory xx00100, data (14), 0

Read Data from Program Memory xx01000, data (14), 0

Increment Address xx0110

Begin Programming xx1000Externally Timed

End Programming xx1110

Bulk Erase Program Memory xx1001Internally Timed

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件