Datasheet 搜索 > 8位微控制器 > Microchip(微芯) > PIC16F627A-E/P 数据手册 > PIC16F627A-E/P 用户编程技术手册 6/22 页

器件3D模型

器件3D模型¥ 22.408

PIC16F627A-E/P 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

8位微控制器

封装:

DIP-18

描述:

MICROCHIP PIC16F627A-E/P 芯片, 微控制器, 8位, PIC16F, 20MHZ, DIP-18

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P2Hot

电气规格在P20

导航目录

PIC16F627A-E/P数据手册

Page:

of 22 Go

若手册格式错乱,请下载阅览PDF原文件

PIC16F627A/628A/648A

DS41196G-page 6 Preliminary © 2007 Microchip Technology Inc.

The optional 16-bit data word will either be an input to,

or an output from the PIC

®

microcontroller, depending

on the command. Load Data commands will be input,

and Read Data commands will be output. The 16-bit

data word only contains 14 bits of data to conform to the

14-bit program memory word. The 14 bits are centered

within the 16-bit word, padded with a leading and trail-

ing zero.

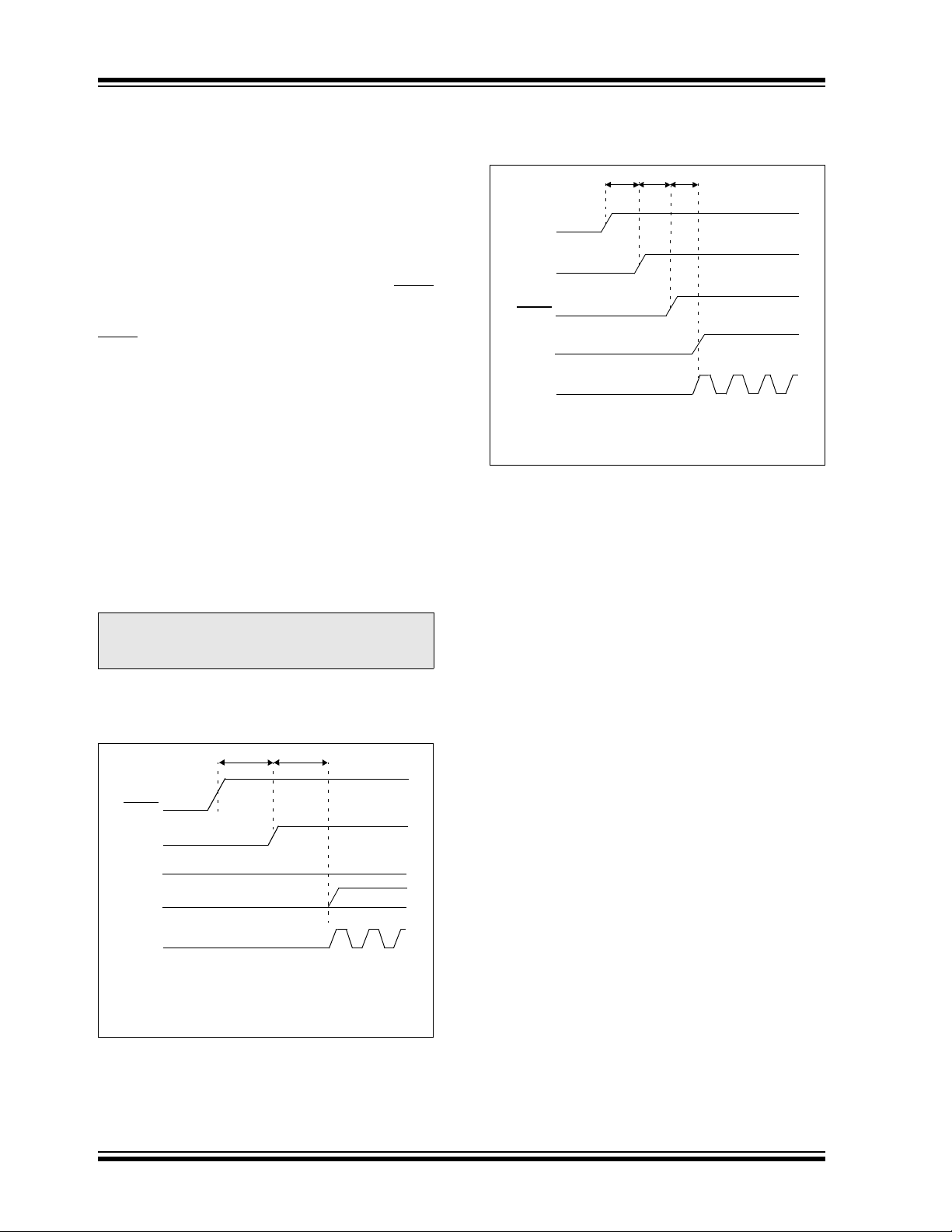

Program/Verify mode may be entered via one of two

methods. High voltage Program/Verify is entered by

holding CLOCK and DATA pins low while raising MCLR

first, then VDD as shown in Figure 2-2. Low voltage

Program/Verify mode is entered by raising V

DD, then

MCLR

and PGM, as shown in Figure 2-3. The PC will

be set to ‘0’ upon entering into Program/Verify mode.

The PC can be changed by the execution of either an

increment PC command, or a Load Configuration

command, which sets the PC to 0x2000.

All other logic is held in the Reset state while in

Program/Verify mode. This means that all I/O are in the

Reset state (high-impedance inputs).

If LVP is not being used for programming and the LVP

Configuration bit is set (i.e., LVP feature is enabled),

the PGM pin must not be allowed to toggle while

programming. The PGM pin is edge sensitive and if an

edge is detected during programming, it may cause the

PC to reset. If the LVP feature is disabled, the PGM pin

will have no effect on programming.

FIGURE 2-2: ENTERING HIGH

VOLTAGE PROGRAM/

VERIFY MODE

FIGURE 2-3: ENTERING LOW

VOLTAGE PROGRAM/

VERIFY MODE

Note: The LVP feature is enabled by default

when the LVP bit of the Configuration

Word is set.

MCLR

VDD

DATA

CLOCK

Tppdp Thld0

LVP

Note: If the LVP fuse is enabled, PGM should be

held low to prevent inadvertent entry into LVP

mode.

VDD

PGM

DATA

CLOCK

Tppdp

MCLR

TlvppThld0

Note: If the device is in LVP mode, raising V

PP to

V

IHH will override LVP mode.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件