Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F8722-I/PT 数据手册 > PIC18F8722-I/PT 用户编程技术手册 5/44 页

器件3D模型

器件3D模型¥ 65.877

PIC18F8722-I/PT 用户编程技术手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-80

描述:

PIC18F8527/8622/8627/8722 8 位微控制器Microchip 的 PIC18F 微控制器是 Microchip 产品线中功能最强大的 8 位设备。 该系列包含的 CAN、LIN 和以太网功能是完整系列外围设备的一部分,可满足嵌入式应用和版本的需求,采用 XLP(极低功耗)技术,用于功耗为关键考量的应用。 Microchip PIC18F8527/8622/8627/8722 系列微控制器是基于 Microchip PIC18 体系结构的 8 位设备,包括了 XLP(极低功率)技术。### 微控制器功能C 语言编译器优化体系结构 软件控制下可自编程 优先级别,用于中断 8 x 8 单周期硬件倍增器 通过两个引脚实现 In-Circuit Serial Programming™ (ICSP™) 通过两个引脚实现在线调试 (ICD) 宽工作电压范围:2.0V 至 5.5V 可编程掉电重置 (BOR),带软件启用选项 延长监控计时器 (WDT) 灵活振荡器结构 ### 电源管理功能运行:CPU 开,外围设备开 空闲:CPU 关,外围设备开 睡眠:CPU 关,外围设备关 超低 50 nA 输入泄漏 运行模式电流低至 25μA 典型值 空闲模式电流低至 6.8μA 典型值 睡眠模式电流低至 120 nA 典型值 计时器 1 振荡器:900 nA,32 kHz,2V 监控计时器:1.6 μA,2V 典型值 双速振荡器启动 ### 外围功能高电流汇电流/源电流 25 mA/25 mA 三个可编程外部中断 四个输入变化中断 三个增强型采集/比较/PWM (ECCP) 模块 两个采集/比较/PWM (CCP) 模块 主同步串行端口 (MSSP) 模块 - 支持 3 线 SPI(所有 4 种模式)和 I2C™ 增强型可寻址 USART 模块组(无需外部晶体) 10 位模拟到数字转换器 - 12 或 16 通道,取决于型号 双模拟比较器,带输入多路复用 可编程 16 级高/低电压检测 (HLVD) 模块 ### PIC18 微控制器展开

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1Hot

电气规格在P40P41

导航目录

PIC18F8722-I/PT数据手册

Page:

of 44 Go

若手册格式错乱,请下载阅览PDF原文件

© 2009 Microchip Technology Inc. DS39643C-page 5

PIC18F872X FAMILY

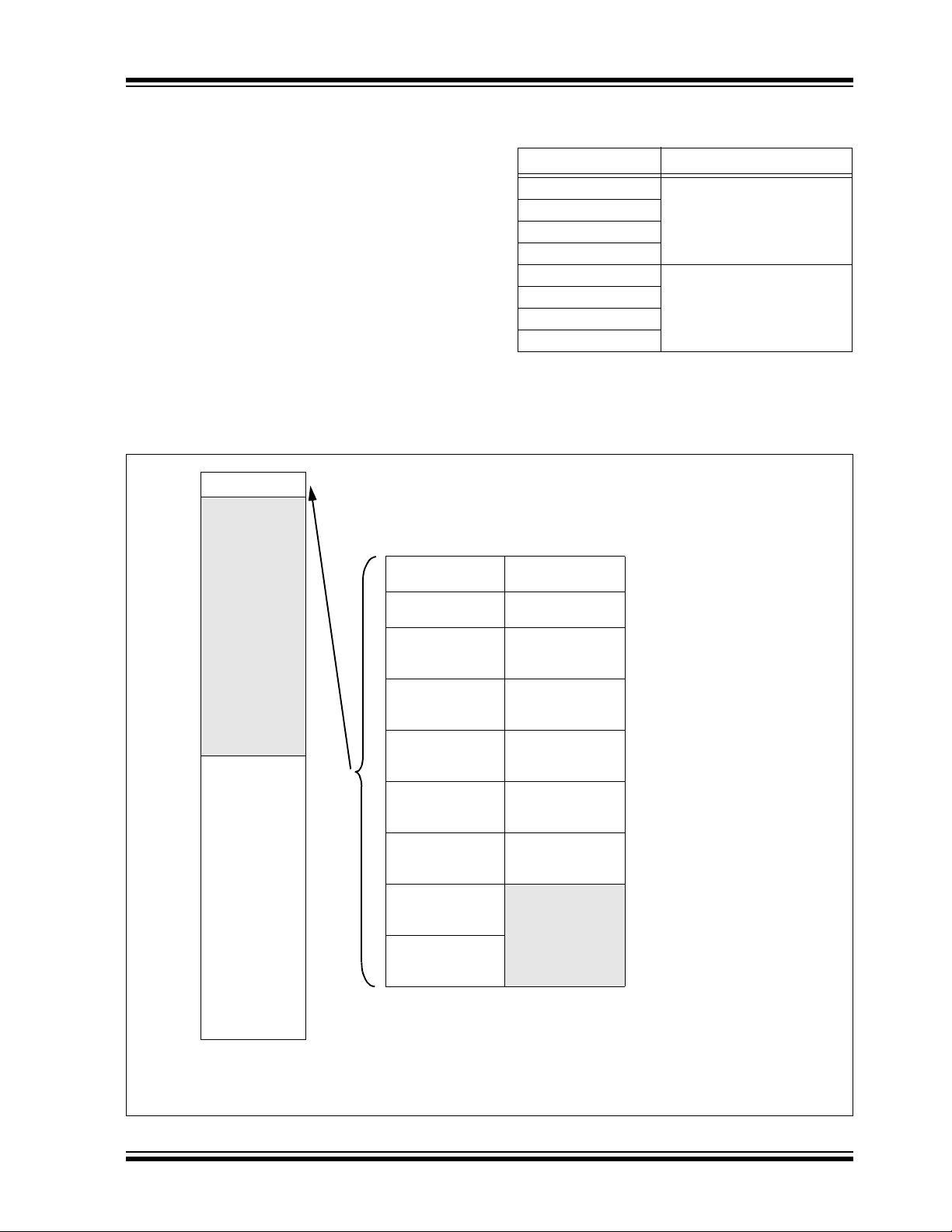

For PIC18F6722/8722/6723/8723 devices, the code

memory space extends from 000000h to 01FFFFh

(128 Kbytes) in eight 16-Kbyte blocks. For

PIC18F6627/8627/6628/8628 devices, the code mem-

ory space extends from 000000h to 017FFFh

(96 Kbytes) in six 16-Kbyte blocks. Addresses, 0000h

through 07FFh, however, define a “Boot Block” region

that is treated separately from Block 0. All of these

blocks define code protection boundaries within the

code memory space.

The size of the Boot Block in PIC18F6627/6722/8627/

8722/8723/8628/6723/6628 devices can be configured

as 1, 2 or 4K words (see Table 5-1). This is done through

the BBSIZ<1:0> bits in the Configuration register,

CONFIG4L. It is important to note that increasing the

size of the Boot Block decreases the size of Block 0.

TABLE 2-3: IMPLEMENTATION OF CODE

MEMORY

FIGURE 2-4: MEMORY MAP AND THE CODE MEMORY SPACE

FOR PIC18F6627/6722/8627/8722/8723/8628/6723/6628 DEVICES

Device Code Memory Size (Bytes)

PIC18F6627

000000h-017FFFh (96K)

PIC18F8627

PIC18F6628

PIC18F8628

PIC18F6722

000000h-01FFFFh (128K)

PIC18F8722

PIC18F6723

PIC18F8723

000000h

200000h

3FFFFFh

01FFFFh

Note: Sizes of memory areas are not to scale.

* Boot Block size is determined by the BBSIZ<1:0> bits in CONFIG4L.

Code Memory

Unimplemented

Read as ‘0’

Configuration

and ID

Space

MEMORY SIZE/DEVICE

128 Kbytes

(PIC18F6722/8722)

96 Kbytes

(PIC18F6627/8627)

Address

Range

Boot Block Boot Block

000000h

0007FFh* or 000FFFh* or 001FFFh*

Block 0 Block 0

000800h* or 001000h* or 002000h*

003FFFh

Block 1 Block 1

004000h

007FFFh

Block 2 Block 2

008000h

00BFFFh

Block 3 Block 3

00C000h

00FFFFh

Block 4 Block 2

010000h

013FFFh

Block 5 Block 5

014000h

017FFFh

Block 6

Unimplemented

Read ‘0’s

018000h

01BFFFh

Block 7

01C000h

01FFFFh

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件