Datasheet 搜索 > FPGA芯片 > Xilinx(赛灵思) > XC2V3000-5FFG1152C 数据手册 > XC2V3000-5FFG1152C 用户编程技术手册 1/11 页

器件3D模型

器件3D模型¥ 0

XC2V3000-5FFG1152C 用户编程技术手册 - Xilinx(赛灵思)

制造商:

Xilinx(赛灵思)

分类:

FPGA芯片

封装:

FCBGA-1152

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

XC2V3000-5FFG1152C数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

DS030 (v1.12) June 20, 2008 www.xilinx.com

Product Specification 1

© Copyright 1998-2008 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and

other countries. All other trademarks are the property of their respective owners.

Features

• Configuration one-time programmable (OTP) read-only

memory designed to store configuration bitstreams for

Spartan

®

, and Spartan-XL FPGAs

• Simple interface to the Spartan device requires only

one user I/O pin

• Programmable reset polarity (active High or active Low)

• Low-power CMOS floating-gate process

• Available in 5V and 3.3V versions

• Available in compact plastic 8-pin DIP, 8-pin VOIC, or

20-pin SOIC packages

• Programming support by leading programmer

manufacturers

• Lead-free (RoHS-compliant) packaging available

• Design support using the Xilinx

®

Alliance and

Foundation™ series software packages

• Guaranteed 20 year life data retention

Introduction

The Spartan family of PROMs provides an easy-to-use,

cost-effective method for storing Spartan device

configuration bitstreams.

When the Spartan device is in Master Serial mode, it

generates a configuration clock that drives the Spartan

FPGA PROM. A short access time after the rising clock

edge, data appears on the PROM DATA output pin that is

connected to the Spartan device D

IN

pin. The Spartan

device generates the appropriate number of clock pulses to

complete the configuration. Once configured, it disables the

PROM. When a Spartan device is in Slave Serial mode, the

PROM and the Spartan device must both be clocked by an

incoming signal.

For device programming, either the Xilinx Alliance or the

Foundation series development systems compiles the

Spartan device design file into a standard HEX format which

is then transferred to most commercial PROM programmers.

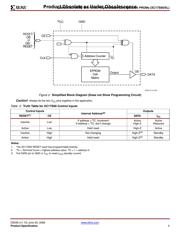

X-Ref Target - Figure 0

Spartan/XL Family One-Time Programmable

Configuration PROMs (XC17S00/XL)

DS030 (v1.12) June 20, 2008 Product Specification

R

Spartan FPGA Configuration Bits Compatible Spartan PROM

XCS05 53,984 XC17S05

XCS05XL 54,544 XC17S05XL

XCS10 95,008 XC17S10

XCS10XL 95,752 XC17S10XL

XCS20 178,144 XC17S20

XCS20XL 179,160 XC17S20XL

XCS30 247,968 XC17S30

XCS30XL 249,168 XC17S30XL

XCS40 329,312 XC17S40

XCS40XL 330,696 XC17S40XL

XC2S50

(1)

559,200 XC17S50XL

XC2S100

(1)

781,216 XC17S100XL

XC2S150

(1)

1,040,096 XC17S150XL

Notes:

1. For new Spartan-II FPGA designs, it is recommended to use the 17S00A family.

Product Obsolete or Under Obsolescence

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件