Datasheet 搜索 > CPLD芯片 > Xilinx(赛灵思) > XC95108-7PC84C 数据手册 > XC95108-7PC84C 用户编程技术手册 1/76 页

器件3D模型

器件3D模型¥ 295.319

XC95108-7PC84C 用户编程技术手册 - Xilinx(赛灵思)

制造商:

Xilinx(赛灵思)

分类:

CPLD芯片

封装:

PLCC-84

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

XC95108-7PC84C数据手册

Page:

of 76 Go

若手册格式错乱,请下载阅览PDF原文件

November 9, 1998 (Version 3.1) 7-3

7

Features

• Complete line of four related Field Programmable Gate

Array product families

- XC3000A, XC3000L, XC3100A, XC3100L

• Ideal for a wide range of custom VLSI design tasks

- Replaces TTL, MSI, and other PLD logic

- Integrates complete sub-systems into a single

package

- Avoids the NRE, time delay, and risk of conventional

masked gate arrays

• High-performance CMOS static memory technology

- Guaranteed toggle rates of 70 to 370 MHz, logic

delays from 7 to 1.5 ns

- System clock speeds over 85 MHz

- Low quiescent and active power consumption

• Flexible FPGA architecture

- Compatible arrays ranging from 1,000 to 7,500 gate

complexity

- Extensive register, combinatorial, and I/O

capabilities

- High fan-out signal distribution, low-skew clock nets

- Internal 3-state bus capabilities

- TTL or CMOS input thresholds

- On-chip crystal oscillator amplifier

• Unlimited reprogrammability

- Easy design iteration

- In-system logic changes

• Extensive packaging options

- Over 20 different packages

- Plastic and ceramic surface-mount and pin-grid-

array packages

- Thin and Very Thin Quad Flat Pack (TQFP and

VQFP) options

• Ready for volume production

- Standard, off-the-shelf product availability

- 100% factory pre-tested devices

- Excellent reliability record

• Complete Development System

- Schematic capture, automatic place and route

- Logic and timing simulation

- Interactive design editor for design optimization

- Timing calculator

- Interfaces to popular design environments like

Viewlogic, Cadence, Mentor Graphics, and others

Additional XC3100A Features

• Ultra-high-speed FPGA family with six members

- 50-85 MHz system clock rates

- 190 to 370 MHz guaranteed flip-flop toggle rates

- 1.55 to 4.1 ns logic delays

• High-end additional family member in the 22 X 22 CLB

array-size XC3195A device

• 8 mA output sink current and 8 mA source current

• Maximum power-down and quiescent current is 5 mA

• 100% architecture and pin-out compatible with other

XC3000 families

• Software and bitstream compatible with the XC3000,

XC3000A, and XC3000L families

XC3100A combines the features of the XC3000A and

XC3100 families:

• Additional interconnect resources for TBUFs and CE

inputs

• Error checking of the configuration bitstream

• Soft startup holds all outputs slew-rate limited during

initial power-up

• More advanced CMOS process

Low-Voltage Versions Available

• Low-voltage devices function at 3.0 - 3.6 V

• XC3000L - Low-voltage versions of XC3000A devices

• XC3100L - Low-voltage versions of XC3100A devices

0

XC3000 Series

Field Programmable Gate Arrays

(XC3000A/L, XC3100A/L)

November 9, 1998 (Version 3.1)

07*

Product Description

R

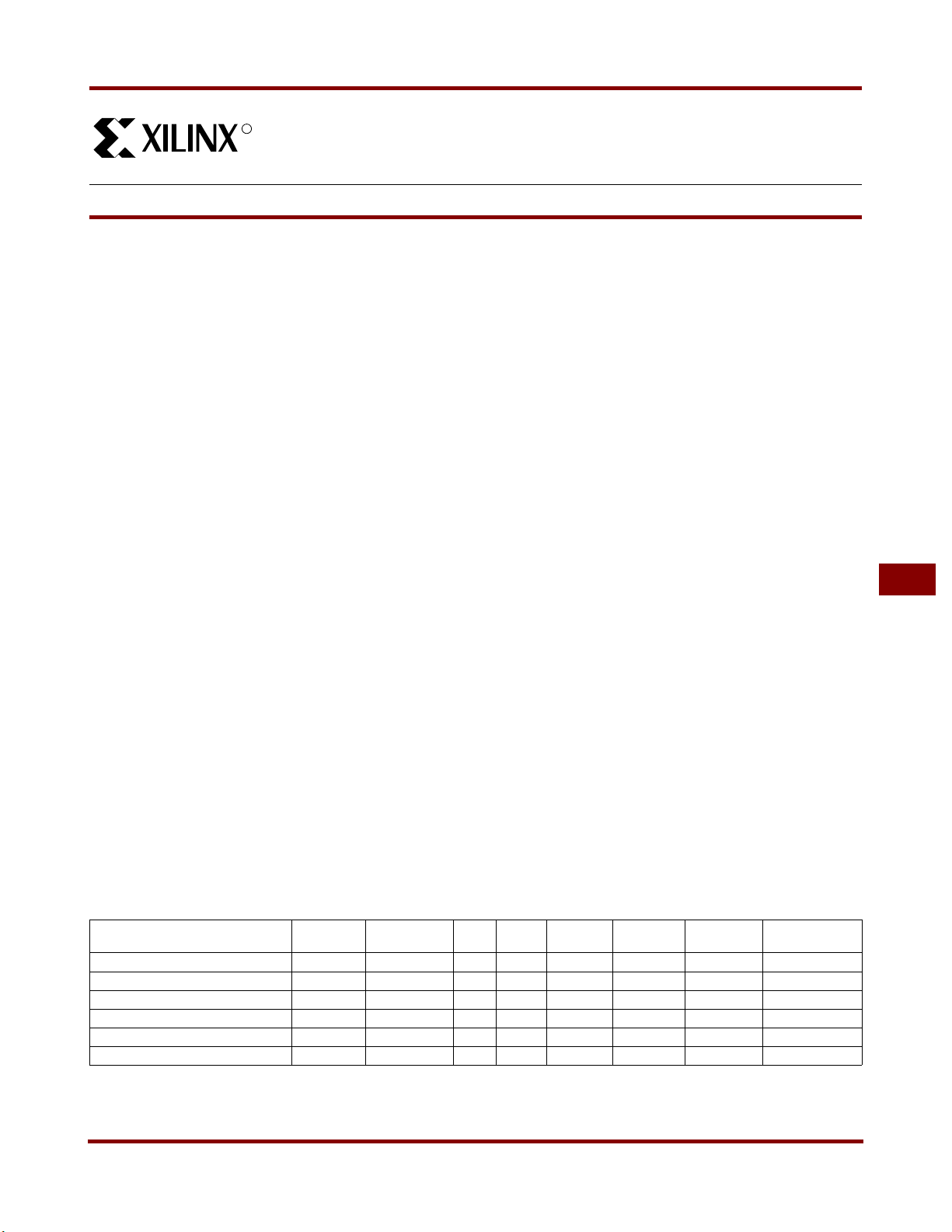

Device

Max Logic

Gates

Typical Gate

Range

CLBs Array

User I/Os

Max

Flip-Flops

Horizontal

Longlines

Configuration

Data Bits

XC3020A, 3020L, 3120A 1,500 1,000 - 1,500 64 8 x 8 64 256 16 14,779

XC3030A, 3030L, 3130A 2,000 1,500 - 2,000 100 10 x 10 80 360 20 22,176

XC3042A, 3042L, 3142A, 3142L 3,000 2,000 - 3,000 144 12 x 12 96 480 24 30,784

XC3064A, 3064L, 3164A 4,500 3,500 - 4,500 224 16 x 14 120 688 32 46,064

XC3090A, 3090L, 3190A, 3190L 6,000 5,000 - 6,000 320 16 x 20 144 928 40 64,160

XC3195A 7,500 6,500 - 7,500 484 22 x 22 176 1,320 44 94,984

Product Obsolete or Under Obsolescence

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件