Datasheet 搜索 > 比较器 > NXP(恩智浦) > 74HC688DB 数据手册 > 74HC688DB 数据手册 2/7 页

器件3D模型

器件3D模型¥ 0

74HC688DB 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

比较器

封装:

SSOP

描述:

8位幅值比较器 8-bit magnitude comparator

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74HC688DB数据手册

Page:

of 7 Go

若手册格式错乱,请下载阅览PDF原文件

December 1990 2

Philips Semiconductors Product specification

8-bit magnitude comparator 74HC/HCT688

FEATURES

• Compare two 8-bit words

• Output capability: standard

• I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT688 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT688 are 8-bit magnitude comparators.

They perform comparison of two 8-bit binary or BCD

words.

The output provides P = Q.

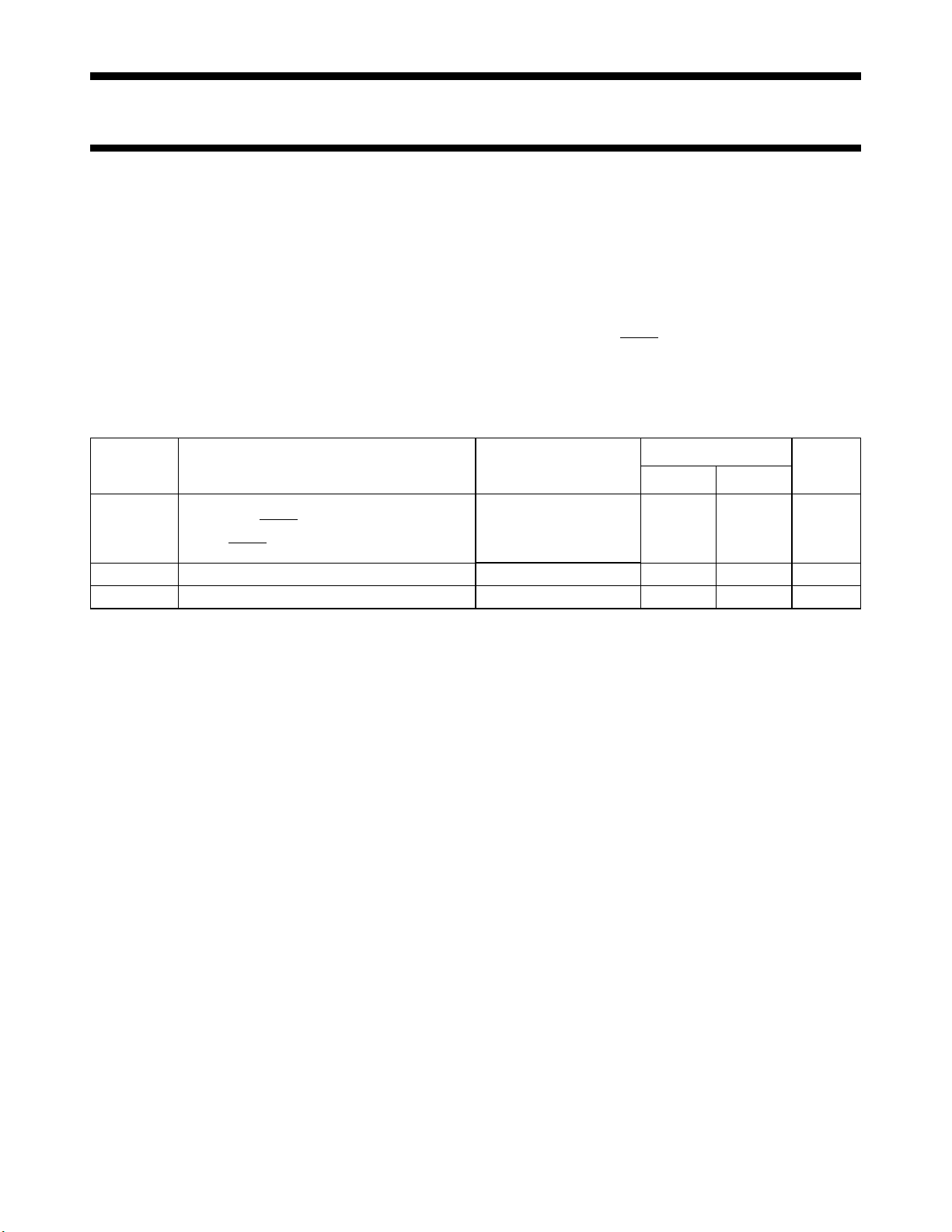

QUICK REFERENCE DATA

GND = 0 V; T

amb

=25°C; t

r

=t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in µW):

P

D

=C

PD

× V

CC

2

× f

i

+ ∑ (C

L

× V

CC

2

× f

o

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

∑ (C

L

× V

CC

2

× f

o

) = sum of outputs

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

− 1.5 V

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL/

t

PLH

propagation delay C

L

= 15 pF; V

CC

=5 V

P

n

, Q

n

to P = Q 1717ns

E to

P = Q 8 12 ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per package notes 1 and 2 30 30 pF

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件