Datasheet 搜索 > 实时时钟芯片 > Maxim Integrated(美信) > DS1337S+C01 数据手册 > DS1337S+C01 数据手册 15/16 页

器件3D模型

器件3D模型¥ 0

DS1337S+C01 数据手册 - Maxim Integrated(美信)

制造商:

Maxim Integrated(美信)

分类:

实时时钟芯片

封装:

SOIC-8

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

DS1337S+C01数据手册

Page:

of 16 Go

若手册格式错乱,请下载阅览PDF原文件

DS1337 I

2

C Serial Real-Time Clock

HANDLING, PC BOARD LAYOUT, AND ASSEMBLY

The DS1337C package contains a quartz tuning-fork crystal. Pick-and-place equipment may be used, but

precautions should be taken to ensure that excessive shocks are avoided. Ultrasonic cleaning should be avoided

to prevent damage to the crystal.

Avoid running signal traces under the package, unless a ground plane is placed between the package and the

signal line. All N.C. (no connect) pins must be connected to ground.

Moisture-sensitive packages are shipped from the factory dry-packed. Handling instructions listed on the package

label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020 standard for

moisture-sensitive device (MSD) classifications.

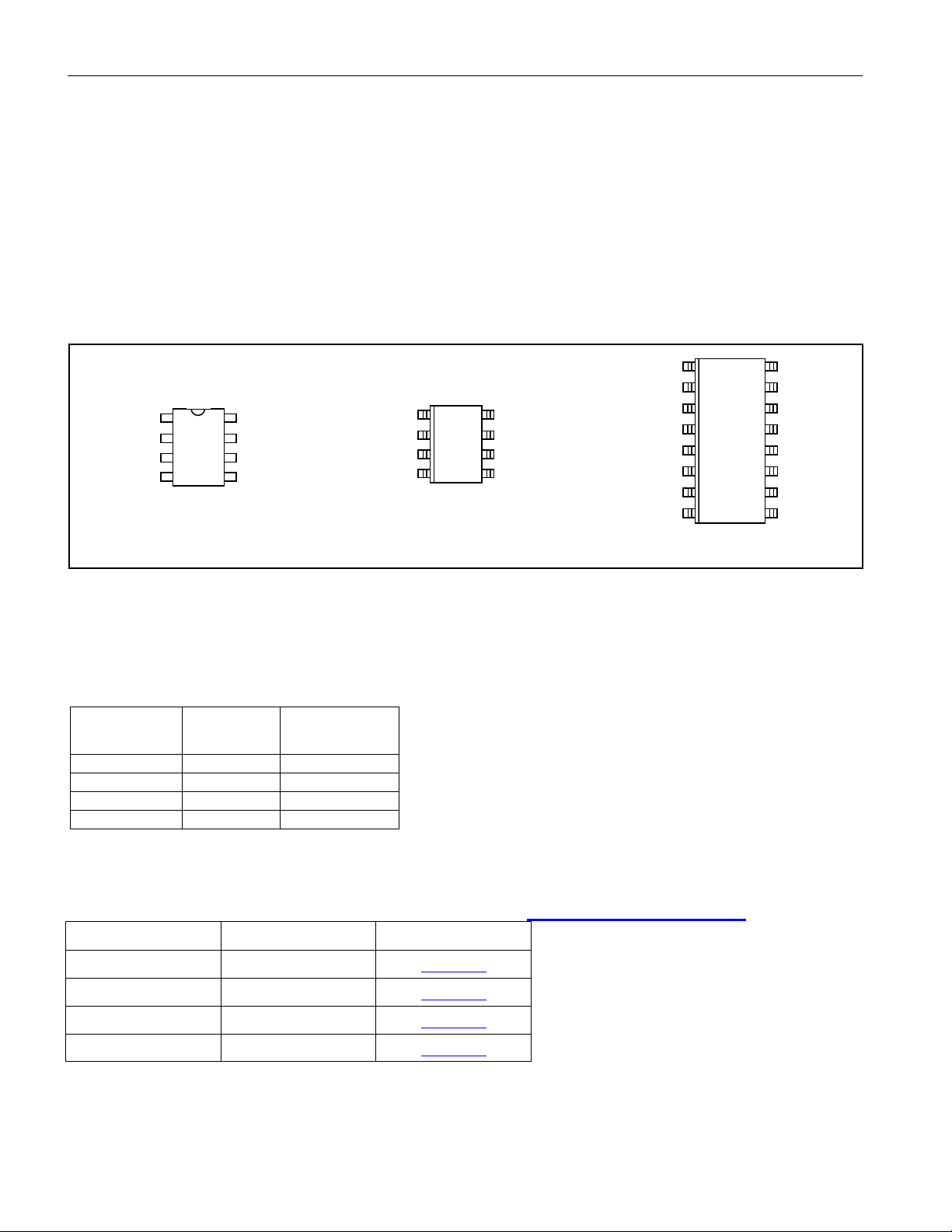

PIN CONFIGURATIONS

CHIP INFORMATION

TRANSISTOR COUNT: 10,950

PROCESS: CMOS

THERMAL INFORMATION

PACKAGE

THETA-J

A

(°C/W)

THETA-J

C

(°C/W)

8 DIP

110

40

8 SO

170

40

8 μSOP

229

39

16 SO

73

23

PACKAGE INFORMATION

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

PACKAGE TYPE

PACKAGE CODE

DOCUMENT NO.

8 PDIP P8+8

21-0043

8 SO S8+2

21-0041

8 µMAX U8+1

21-0036

16 SO W16-H2

21-0042

TOP VIEW

DIP

INTA

X1

X2

GND

V

CC

SCL

SDA

SQW/INTB

DS1337

SO, µSOP

X1

X2

GND

V

CC

SCL

SDA

SQW/INTB

INTA

DS1337

SQW/INTB

SCL

SDA

GND

INTA

V

CC

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

DS1337C

SO (300 mils)

15 of 16

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件